### IOWA STATE UNIVERSITY Digital Repository

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2017

# Low-cost, high-precision DAC design based on ordered element matching and verification against undesired operating points for analog circuits

You Li Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Li, You, "Low-cost, high-precision DAC design based on ordered element matching and verification against undesired operating points for analog circuits" (2017). *Graduate Theses and Dissertations*. 17249. https://lib.dr.iastate.edu/etd/17249

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

### Low-cost, high-precision DAC design based on ordered element matching and verification against undesired operating points for analog circuits

by

### You Li

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

Major: Electrical Engineering

Program of Study Committee: Degang Chen, Major Professor Nathan M. Neihart Chris Chong-Nuen Chu Zhengdao Wang Jaeyoun (Jay) Kim

Iowa State University

Ames, Iowa

2017

Copyright © You Li, 2017. All rights reserved.

### DEDICATION

To my family

### TABLE OF CONTENTS

| LIST ( | OF TABLES                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| LIST ( | OF FIGURES                                                                                                                        |

| ACKN   | OWLEDGEMENTS                                                                                                                      |

| ABST   | $\mathbf{RACT} \dots \dots$ |

| CHAP   | TER 1. INTRODUCTION 1                                                                                                             |

| 1.1    | Background                                                                                                                        |

| 1.2    | Contribution of this Dissertation                                                                                                 |

| 1.3    | Organization of this Dissertation                                                                                                 |

| CHAP   | TER 2. LOW-COST, HIGH-PRECISION DAC DESIGN BASED                                                                                  |

| ON     | ORDERED ELEMENT MATCHING                                                                                                          |

| 2.1    | Introduction                                                                                                                      |

| 2.2    | Low-cost, High-precision DAC Structure Based on Ordered Element Matching . 9                                                      |

|        | 2.2.1 OEM Technology                                                                                                              |

|        | 2.2.2 High-precision DAC Structure 10                                                                                             |

|        | 2.2.3 Segmentation Choices                                                                                                        |

| 2.3    | Gain Calibration Pseudo DAC Design 15                                                                                             |

|        | 2.3.1 Gain Error between Different Segments 15                                                                                    |

|        | 2.3.2 Gain Calibration DAC                                                                                                        |

|        | 2.3.3 Implementation of Gain Calibration 19                                                                                       |

| 2.4    | OEM Calibration                                                                                                                   |

|        | 2.4.1 OEM Calibration                                                                                                             |

|        | 2.4.2 Digital Circuits to Implement OEM Calibration                                                                               |

| 2.5  | Behav  | vioral Simulation Results                                      | 26 |

|------|--------|----------------------------------------------------------------|----|

| 2.6  | Concl  | usion                                                          | 33 |

| CHAP | TER 3  | 3. DESIGN AND MEASUREMENT OF A HIGH-PRECISION                  |    |

| DA   | C IN   | 130 NM CMOS TECHNOLOGY                                         | 34 |

| 3.1  | Introd | luction                                                        | 34 |

| 3.2  | DAC    | Design in GF 130 nm Process                                    | 35 |

|      | 3.2.1  | Behavioral Model and Schematic Design                          | 35 |

|      | 3.2.2  | Layout Design                                                  | 42 |

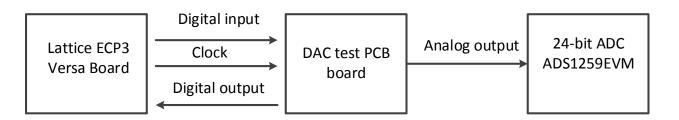

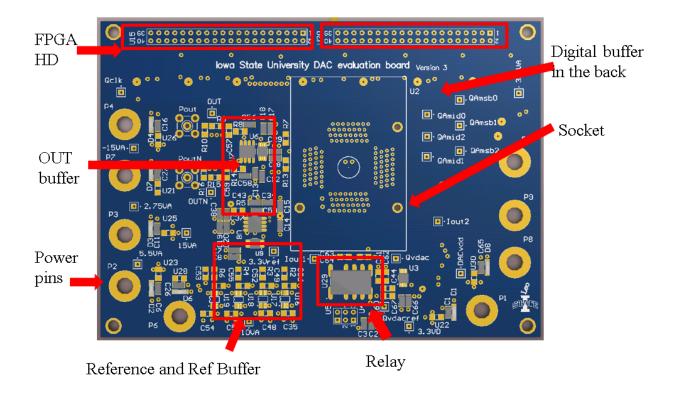

| 3.3  | Test S | Scheme and Test Board Design                                   | 49 |

|      | 3.3.1  | Test Scheme                                                    | 49 |

|      | 3.3.2  | Test Board Design                                              | 49 |

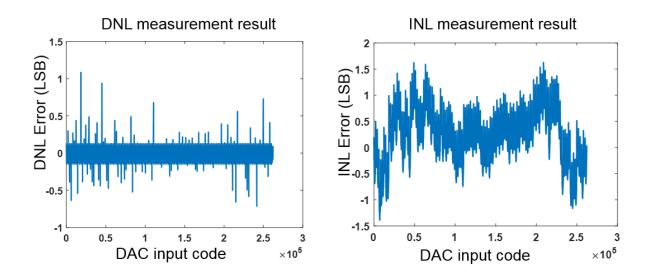

| 3.4  | Measu  | rement Results                                                 | 52 |

| 3.5  | Concl  | usion                                                          | 56 |

| CHAP | TER 4  | 4. EFFICIENT VERIFICATION AGAINST UNDESIRED OP-                |    |

| ER   |        | G POINTS FOR MOS ANALOG CIRCUITS                               | 57 |

| 4.1  | Introd | luction                                                        | 57 |

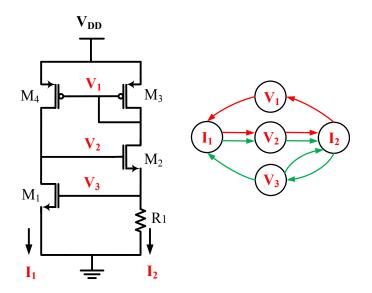

| 4.2  | Feedl  | back Loop Finding and Sign Determination                       | 61 |

|      | 4.2.1  | Convert Circuit Netlist to Graph                               | 61 |

|      | 4.2.2  | Determine the Signs of Feedback Loops                          | 62 |

| 4.3  | PFLs   | Breaking and Return Function                                   | 65 |

|      | 4.3.1  | Break PFLs and Obtain a Return Function                        | 65 |

|      | 4.3.2  | Monotonic Return Function                                      | 66 |

|      | 4.3.3  | Definitions and Theorems for General Return Function           | 68 |

|      | 4.3.4  | Definitions and Theorems for Monotonic Return Function         | 70 |

|      | 4.3.5  | Verification for Different Types of Return Functions           | 71 |

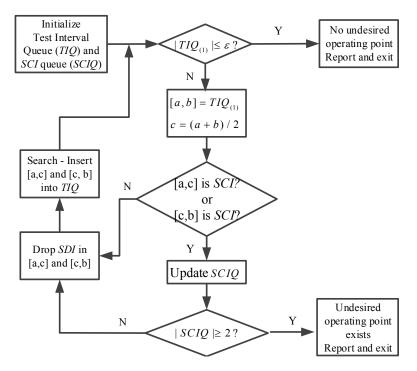

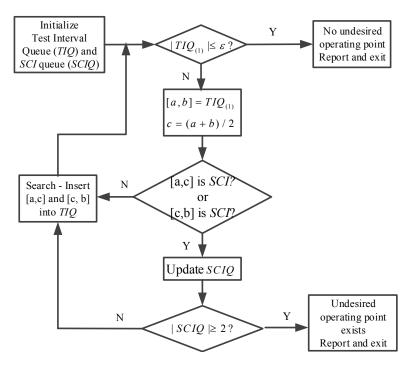

| 4.4  | Divide | e and Contraction Algorithms for Monotonic Return Function     | 72 |

|      | 4.4.1  | Monotonic Divide and Contraction (MDC) Algorithm               | 72 |

|      | 4.4.2  | User-defined Monotonic Divide and Contraction (UMDC) Algorithm | 73 |

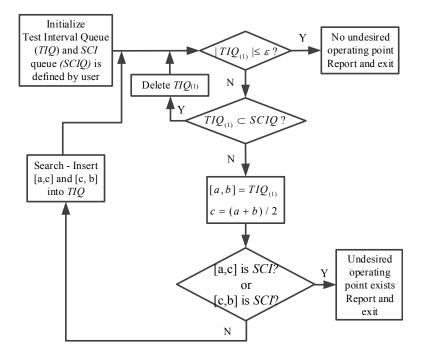

| 4.5  | Divide | $\mathbf e$ and Contraction Algorithms for Non-monotonic Return Function   | 75  |

|------|--------|----------------------------------------------------------------------------|-----|

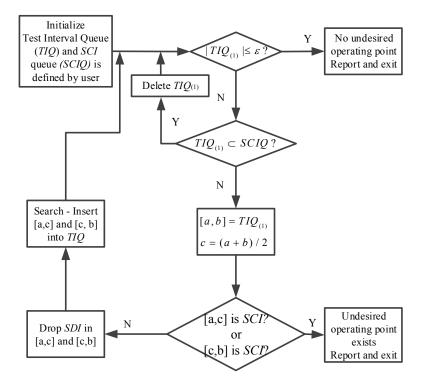

|      | 4.5.1  | General Divide and Contraction (GDC) Algorithm                             | 76  |

|      | 4.5.2  | User-defined General Divide and Contraction (UGDC) Algorithm               | 76  |

| 4.6  | Simula | ation Results                                                              | 77  |

| 4.7  | Discus | ssion                                                                      | 81  |

| 4.8  | Conclu | usion                                                                      | 85  |

| CHAP | TER 5  | 5. TWO DIMENSIONAL ANALOG VERIFICATIONS AGAINS                             | Г   |

| UN   | DESI   | RED OPERATING POINTS FOR MOS ANALOG CIRCUITS                               | 86  |

| 5.1  | Introd | uction                                                                     | 86  |

| 5.2  | Two I  | Dimensional Analog Verification Problems                                   | 89  |

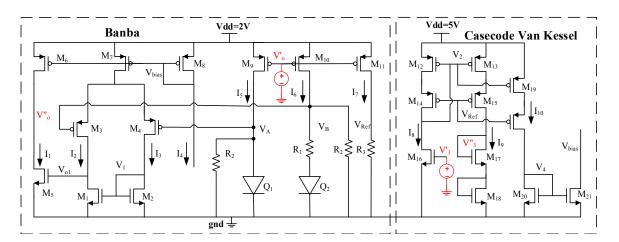

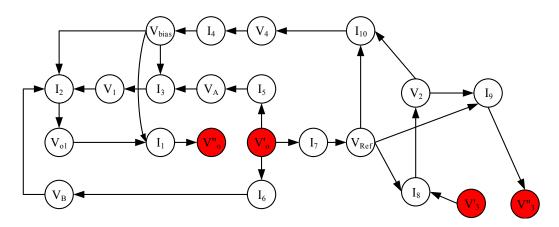

|      | 5.2.1  | B1P and B2P circuits                                                       | 89  |

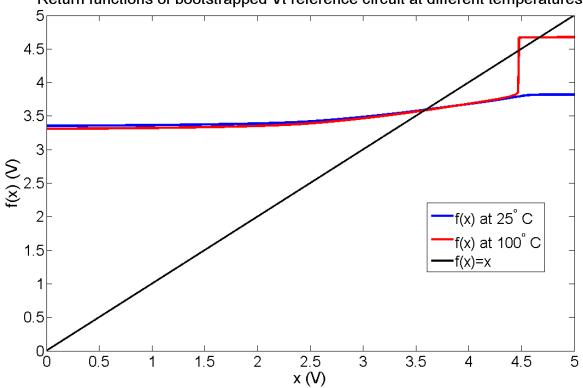

|      | 5.2.2  | Existence of Undesired Operating Points with Temperature Variation .       | 90  |

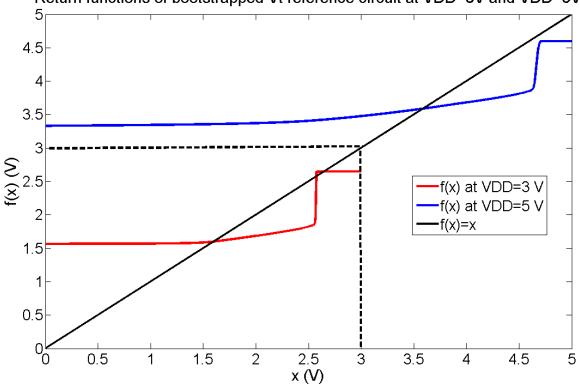

|      | 5.2.3  | Existence of Undesired Operating Points with Voltage Supply Variation      | 91  |

|      | 5.2.4  | Existence of Undesired Operating Points with Process Variations            | 92  |

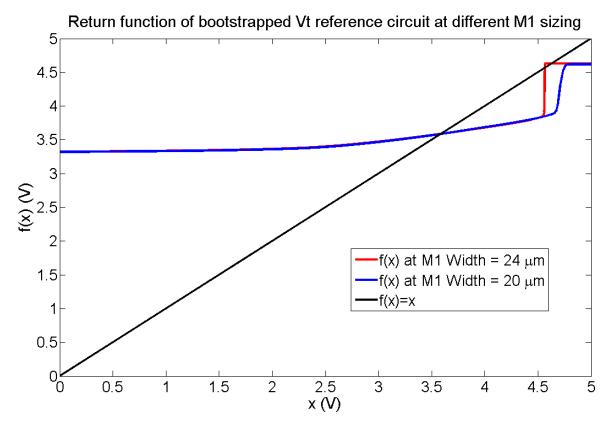

|      | 5.2.5  | Existence of Undesired Operating Points with Transistor Sizing             | 92  |

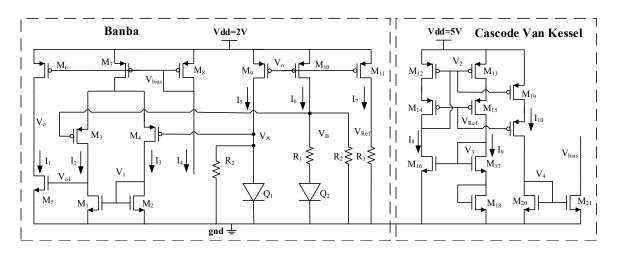

|      | 5.2.6  | Existence of Undesired Operating Points in B2P Circuits                    | 93  |

| 5.3  | Two I  | Dimensional Vector Fields                                                  | 94  |

| 5.4  | Applic | cation of Two Dimensional Vector Fields to Analog Verification             | 98  |

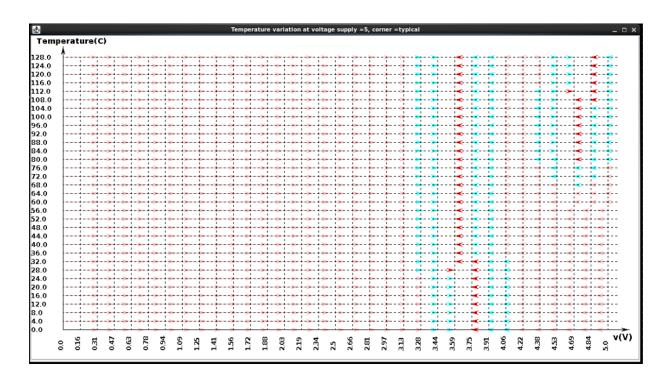

|      | 5.4.1  | Two Dimensional Vector Fields for Temperature Verification $\ldots \ldots$ | 98  |

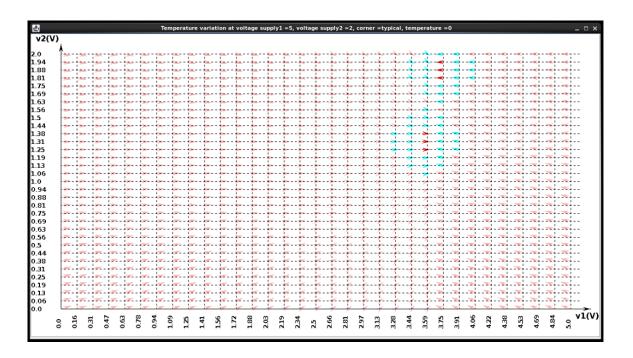

|      | 5.4.2  | Two Dimensional Vector Fields for Voltage Supply Variation $\ . \ . \ .$ . | 99  |

|      | 5.4.3  | Two Dimensional Vector Fields for Transistor Sizing                        | 101 |

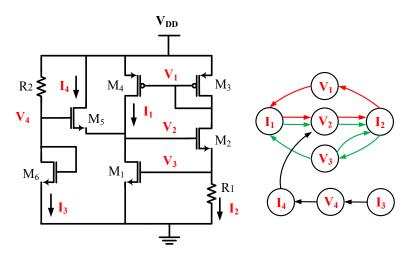

|      | 5.4.4  | Two Dimensional Vector Fields for B2P Circuits                             | 101 |

| 5.5  | Applic | cation Examples                                                            | 102 |

|      | 5.5.1  | Analog Verification with PVT Variation                                     | 103 |

|      | 5.5.2  | Analog Verification with Two Dimensional Circuits                          | 103 |

| 5.6  | Conclu | usion                                                                      | 104 |

CHAPTER 6. ITV: A NEW VERIFICATION TOOL TO IDENTIFY UN-

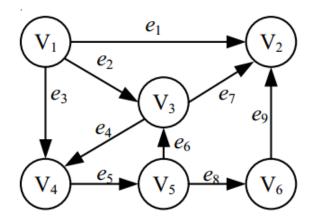

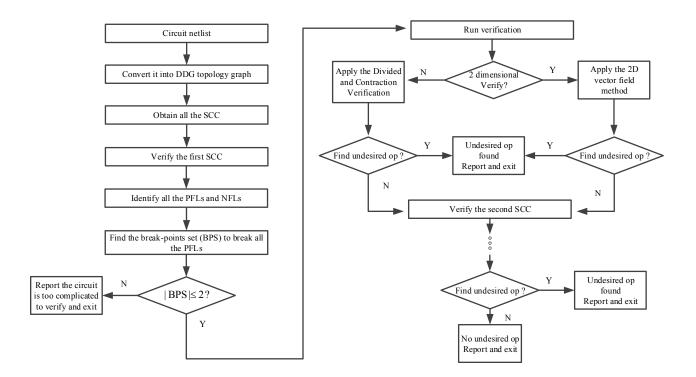

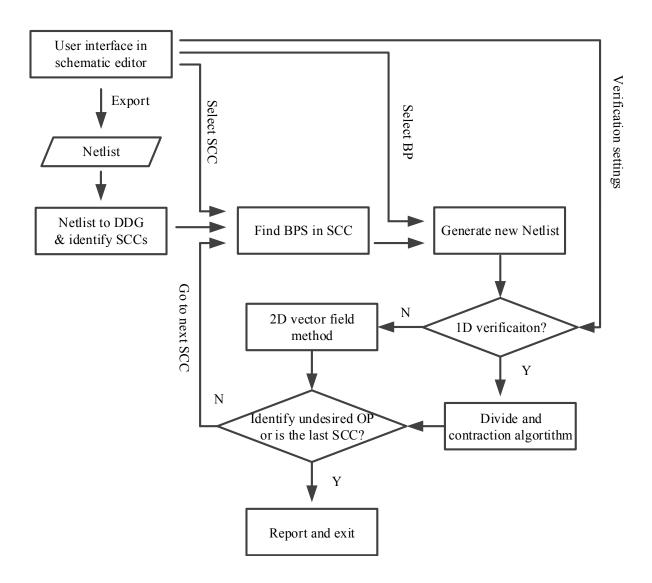

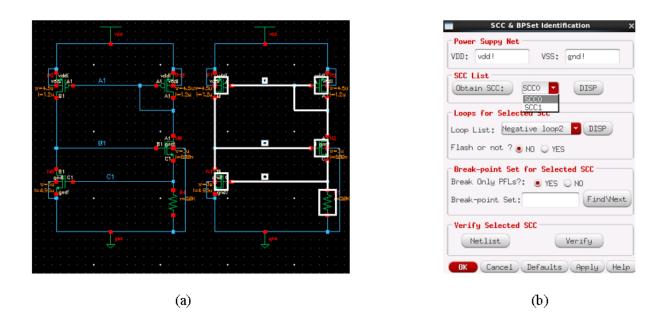

#### DESIRED OPERATING POINTS IN ANALOG AND MIXED-SIGNAL 6.11066.2Proposed Verification Flow 1076.2.1Strongly Connected Component (SCC) 1086.2.21096.2.3Verification Flow 109Tool Implementation 109 6.36.3.1ITV Flow 110 6.3.2111

|       | 6.3.3  | Implementation of Loop Identification and Break           | 112 |

|-------|--------|-----------------------------------------------------------|-----|

|       | 6.3.4  | Implementation of Divide and Contraction Algorithms       | 113 |

|       | 6.3.5  | Implementation of the Two Dimensional Vector Field Method | 113 |

| 6.4   | ITV U  | sage                                                      | 114 |

|       | 6.4.1  | Loop Identification and Break                             | 114 |

|       | 6.4.2  | Run Verification Settings                                 | 117 |

| 6.5   | ITV II | nstallation, Program Files and Demo Circuits              | 123 |

|       | 6.5.1  | ITV Installation                                          | 124 |

|       | 6.5.2  | Program Files in ITV                                      | 125 |

|       | 6.5.3  | Demo Circuits in ITV                                      | 126 |

| 6.6   | Conclu | usion                                                     | 126 |

| CHAP  | TER 7  | CONCLUSION                                                | 128 |

| BIBLI | OGRA   | РНҮ                                                       | 130 |

### LIST OF TABLES

| Table 2.1 | OEM Reduction Factor                                                  | 14  |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2.2 | Area of a 9-bit CalDAC                                                | 22  |

| Table 2.3 | Digital Coding for OEM Binarization (7-bit)                           | 25  |

| Table 2.4 | Simulation Results of Area Comparison                                 | 32  |

| Table 3.1 | The Calibration DAC (CalDAC) Design                                   | 37  |

| Table 3.2 | The Switch Design                                                     | 38  |

| Table 3.3 | MATLAB and Schematic Simulation Result                                | 40  |

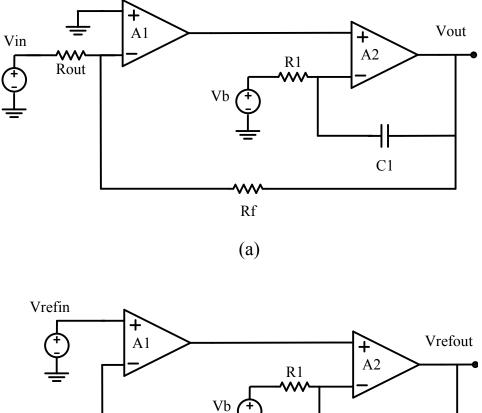

| Table 3.4 | Key Specifications of A1 and A2                                       | 51  |

| Table 3.5 | Measurement Results                                                   | 53  |

| Table 3.6 | Area Comparison                                                       | 54  |

| Table 3.7 | Noise Performance of the ADS1259EVM                                   | 56  |

| Table 4.1 | The Signs of Different Dependencies for MOSFETs                       | 62  |

| Table 4.2 | Simulation Results of Bootstrapped Vt Reference Circuit               | 79  |

| Table 4.3 | Simulation Results of Bootstrapped Vt Reference With Start-up Circuit | 80  |

| Table 4.4 | Simulation Results of Self-biased Banba Bandgap Reference Circuit     | 83  |

| Table 5.1 | Simulation Results of Bootstrapped Vt Reference With PVT Variations   | 103 |

| Table 5.2 | Simulation Results of the Van Kessel-Banba Circuit                    | 105 |

### LIST OF FIGURES

| Figure 2.1  | OEM Binarization                                                    | 10 |

|-------------|---------------------------------------------------------------------|----|

| Figure 2.2  | Proposed OEM Based High-precision DAC Structure                     | 11 |

| Figure 2.3  | (a) First Simplified CalDAC Structure; (b) Second Simplified CalDAC |    |

|             | Structure.                                                          | 17 |

| Figure 2.4  | CalDAC Range                                                        | 19 |

| Figure 2.5  | CalDAC Implemented As a Sub-radix-2 DAC                             | 20 |

| Figure 2.6  | CalDAC Ratio                                                        | 20 |

| Figure 2.7  | The Gain Calibration Process                                        | 21 |

| Figure 2.8  | OEM Calibration Process: (a) Application of OEM Binarization to the |    |

|             | MSB Segment; (b) Application of OEM Binarization to the ISB Segment | 24 |

| Figure 2.9  | OEM Calibration Circuits                                            | 26 |

| Figure 2.10 | (a) INL Plot of the Original 13-bit LSB and ISB Segments; (b) DNL   |    |

|             | Plot of the Original 13-bit LSB and ISB Segments                    | 27 |

| Figure 2.11 | (a) INL Plot of the 13-bit LSB and ISB Segments After Applying OEM  |    |

|             | Binarization to the ISB Segment; (b) DNL Plot of the 13-bit LSB and |    |

|             | ISB Segments After Applying OEM Binarization to the ISB Segment     | 28 |

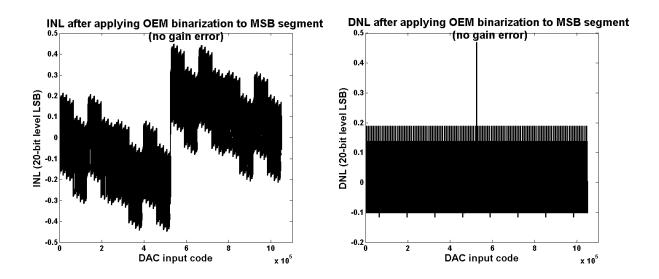

| Figure 2.12 | (a) INL Plot of the 20-bit DAC After Adding the MSB Segment Without |    |

|             | Gain Error; (b) DNL Plot of the 20-bit DAC After Adding the MSB     |    |

|             | Segment Without Gain Error                                          | 29 |

| Figure 2.13 | (a) INL Plot of the 20-bit DAC After Applying OEM Binarization to   |    |

|             | the MSB Segment Without Gain Error; (b) DNL Plot of the 20-bit DAC  |    |

|             | After Applying OEM Binarization to the MSB Segment Without Gain     |    |

|             | Error                                                               | 29 |

www.manaraa.com

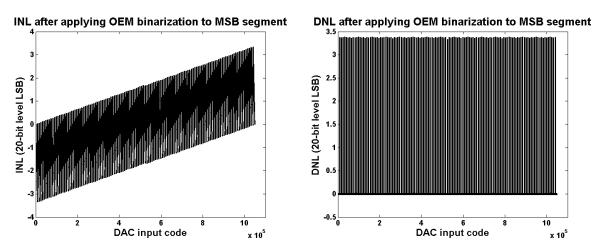

| Figure 2.14 | (a) INL Plot of the 20-bit DAC After Applying OEM Binarization to       |    |

|-------------|-------------------------------------------------------------------------|----|

|             | the MSB Segment With Positive Gain Error; (b) DNL Plot of the 20-       |    |

|             | bit DAC After Applying OEM Binarization to the MSB Segment With         |    |

|             | Positive Gain Error                                                     | 30 |

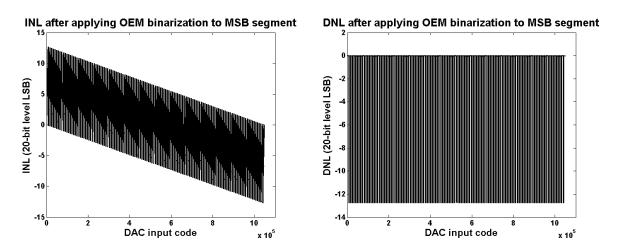

| Figure 2.15 | (a) INL Plot of the 20-bit DAC After Applying OEM Binarization to       |    |

|             | the MSB Segment With Negative Gain Error; (b) DNL Plot of the 20-       |    |

|             | bit DAC After Applying OEM Binarization to the MSB Segment With         |    |

|             | Negative Gain Error                                                     | 31 |

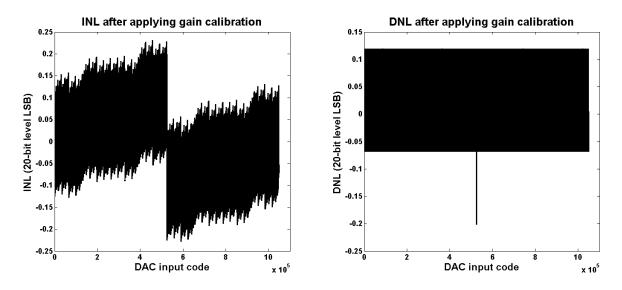

| Figure 2.16 | (a) INL Plot of the 20-bit DAC After Gain Calibration; (b) DNL Plot     |    |

|             | of the 20-bit DAC After Gain Calibration                                | 31 |

| Figure 2.17 | DNL and INL Distribution Comparison of 1,000 Randomly Generated         |    |

|             | Resistor Arrays in a 20-bit R-2R DAC With $\sigma_{R_{msb}} = 4.7e - 4$ | 32 |

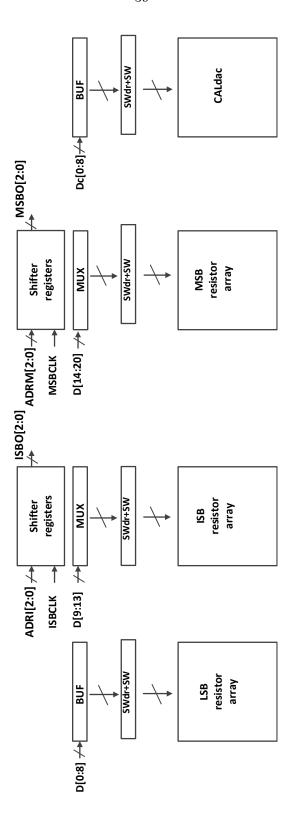

| Figure 3.1  | Block Diagram of the DAC                                                | 39 |

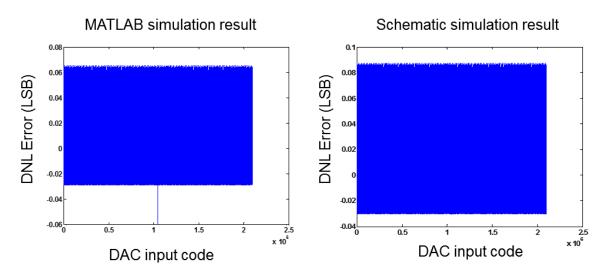

| Figure 3.2  | MATLAB and Schematic DNL Simulation Results                             | 41 |

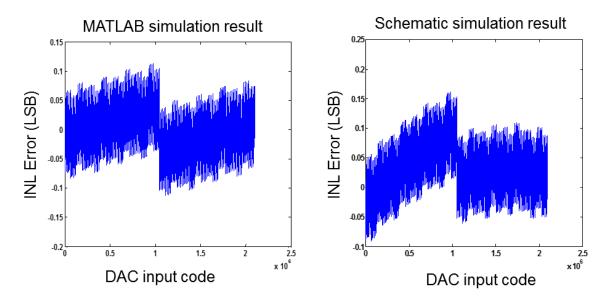

| Figure 3.3  | MATLAB and Schematic INL Simulation Results                             | 41 |

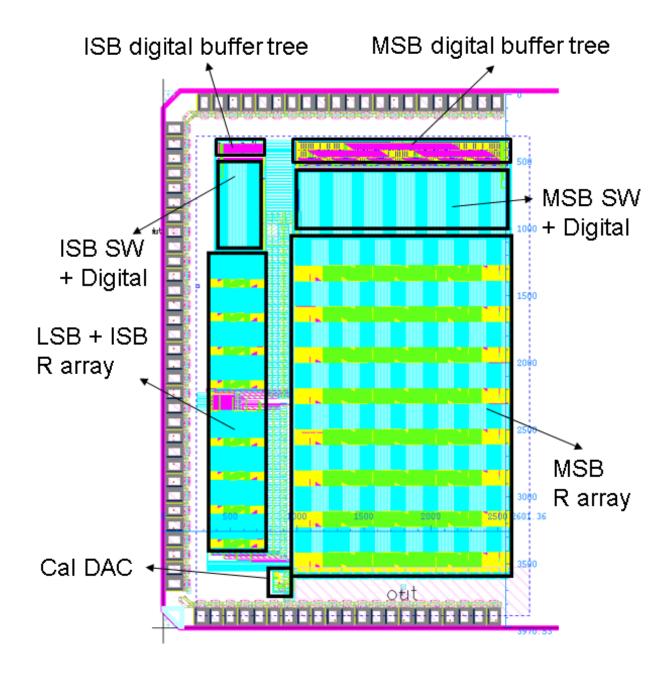

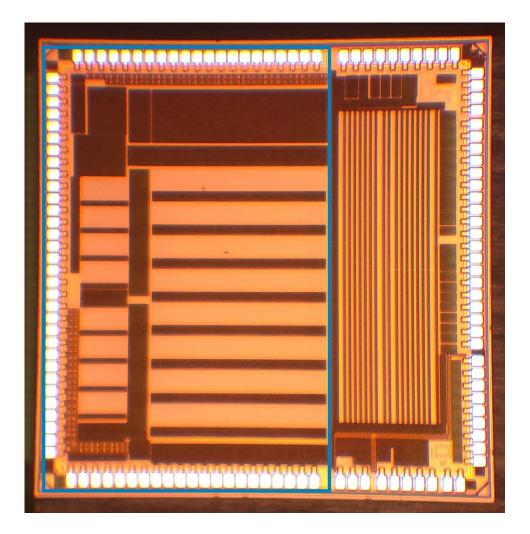

| Figure 3.4  | The Top Level Layout                                                    | 43 |

| Figure 3.5  | The Die Photograph of the Whole Chip                                    | 44 |

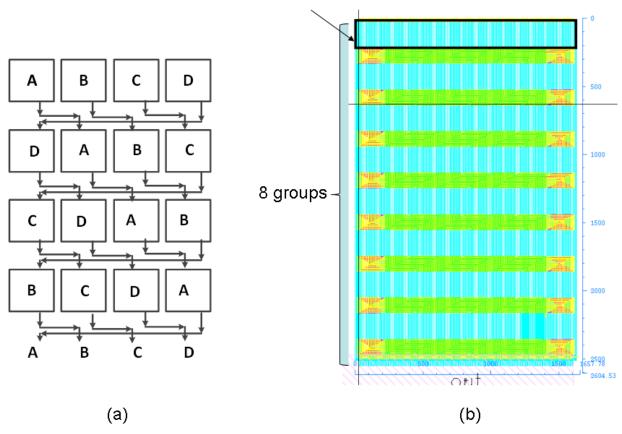

| Figure 3.6  | (a)2nd Order Common Centroid Layout Example; (b)Layout of the           |    |

|             | MSB Segment                                                             | 45 |

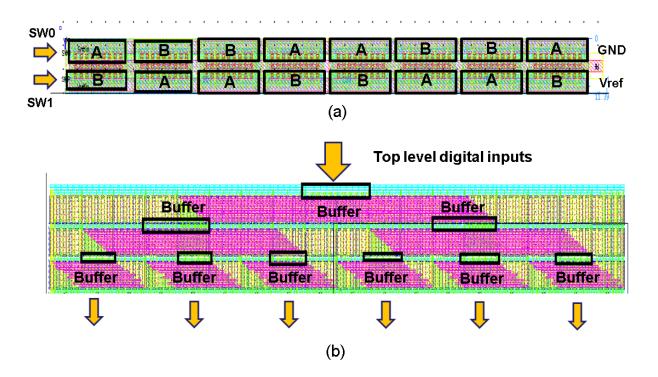

| Figure 3.7  | (a)Common Centroid Layout for a Switch Pair; (b)A Digital Signal        |    |

|             | Buffer Tree                                                             | 46 |

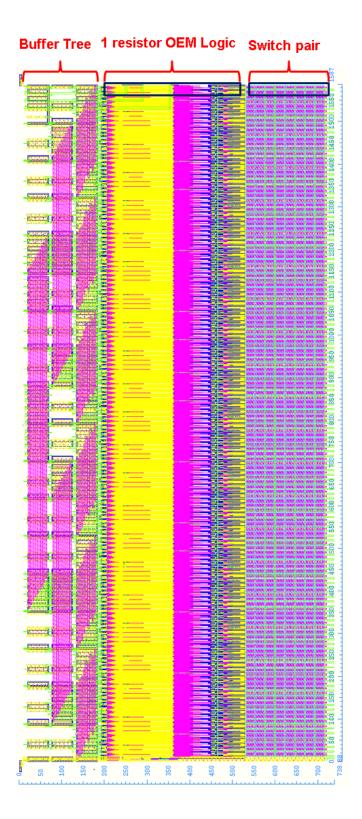

| Figure 3.8  | Layout of One-resistor OEM Logic                                        | 47 |

| Figure 3.9  | Layout of MSB Buffer Tree, Digital Circuits and Switches                | 48 |

| Figure 3.10 | The Top Level Test Scheme                                               | 49 |

| Figure 3.11 | (a)Output Buffer Design for DAC Tests; (b)Reference Buffer Design for   |    |

|             | DAC Tests                                                               | 50 |

| Figure 3.12 | The Whole Test PCB Board                                                | 52 |

| Figure 3.13 | The Measurement Results                                                 | 53 |

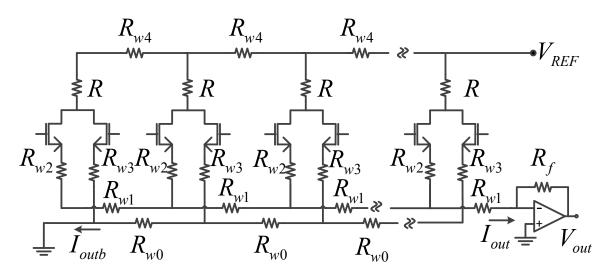

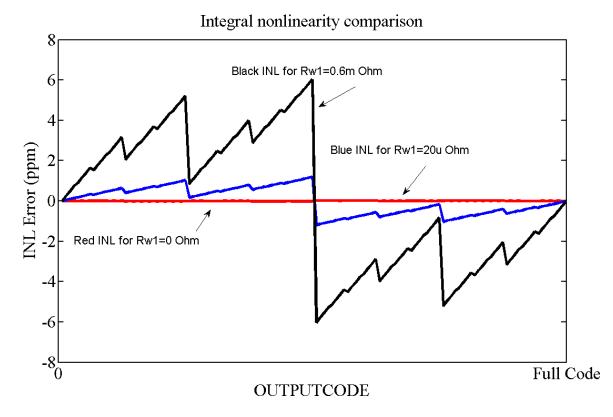

| Figure 3.14 | Simplified DAC Structure With Wire Resistance                            | 55 |

|-------------|--------------------------------------------------------------------------|----|

| Figure 3.15 | INL Performance Comparison for DAC With and Without Wire Resis-          |    |

|             | tance                                                                    | 55 |

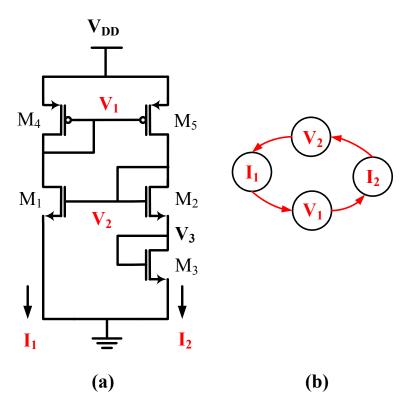

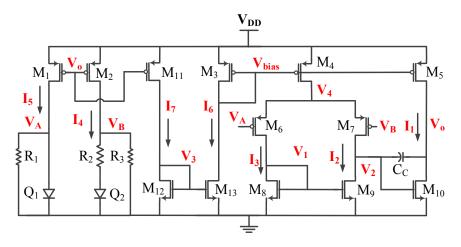

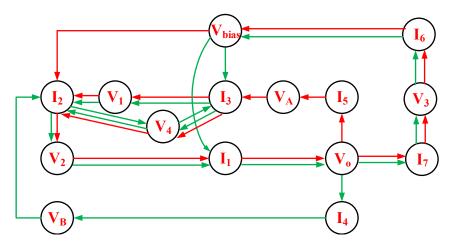

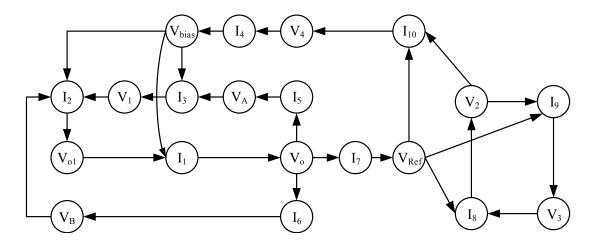

| Figure 4.1  | (a) Inv-Widlar Circuit; (b) Circuit Graph for Inv-Widlar Circuit         | 62 |

| Figure 4.2  | Analyzing the Sign of Dependency for Drain-source Current to Source/Dra  | in |

|             | Voltage in a NMOS                                                        | 64 |

| Figure 4.3  | Circuit Graph for Inv-Widlar Showing the Break-loop Homotopy             | 66 |

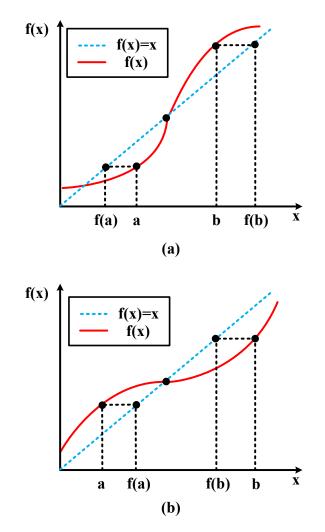

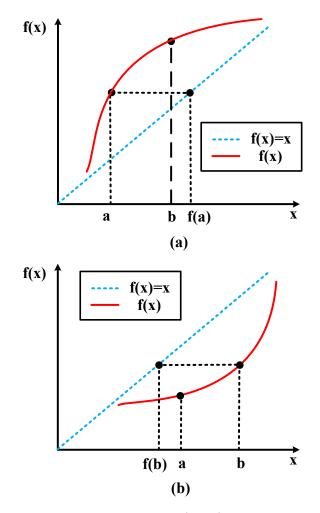

| Figure 4.4  | (a) Signal Map of a Return Function Without NFL; (b) Signal Map of       |    |

|             | a Return Function With NFL                                               | 67 |

| Figure 4.5  | Examples of Sign Change Interval $(SCI)$ With Monotonic Return Func-     |    |

|             | tion                                                                     | 69 |

| Figure 4.6  | Examples of Sign Definite Interval $(SDI)$ With Monotonic Return Func-   |    |

|             | tion                                                                     | 70 |

| Figure 4.7  | Flow Chart of the MDC Algorithm                                          | 74 |

| Figure 4.8  | Flow Chart of the UMDC Algorithm.                                        | 75 |

| Figure 4.9  | Flow Chart of the GDC Algorithm.                                         | 76 |

| Figure 4.10 | Flow Chart of the UGDC Algorithm.                                        | 77 |

| Figure 4.11 | Circuit Graph for the Bootstrapped Vt Reference Circuit.                 | 78 |

| Figure 4.12 | Circuit Graph for the Bootstrapped Vt Reference Circuit With Start-up    |    |

|             | Circuit.                                                                 | 80 |

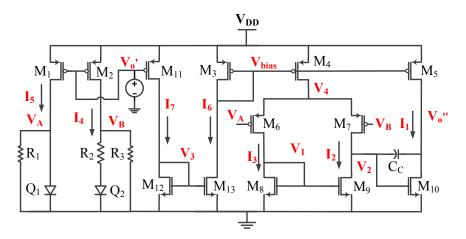

| Figure 4.13 | Self-biased Banba Bandgap Reference Circuit.                             | 81 |

| Figure 4.14 | Circuit Graph of the Self-biased Banba Bandgap Reference Circuit $\ .$ . | 82 |

| Figure 4.15 | Implementation of Breaking Loop of the Self-biased Banba Bandgap         |    |

|             | Reference Circuit                                                        | 82 |

| Figure 5.1  | Break the Bootstrapped Vt Reference Circuit                              | 90 |

| Figure 5.2  | Return Functions of the Bootstrapped Vt Reference Circuit at Different   |    |

|             | Temperatures                                                             | 91 |

| Figure 5.3  | Return Functions of the Bootstrapped Vt Reference Circuit at VDD= $3V$   |     |

|-------------|--------------------------------------------------------------------------|-----|

|             | and VDD=5V                                                               | 92  |

| Figure 5.4  | Return Functions of the Bootstrapped Vt Reference Circuit at Different   |     |

|             | M1 Sizing                                                                | 93  |

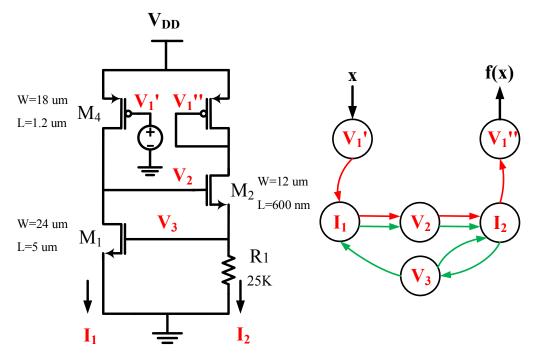

| Figure 5.5  | Van Kessel-Banba Circuit                                                 | 94  |

| Figure 5.6  | Circuit Graph of Van Kessel-Banba Circuit                                | 94  |

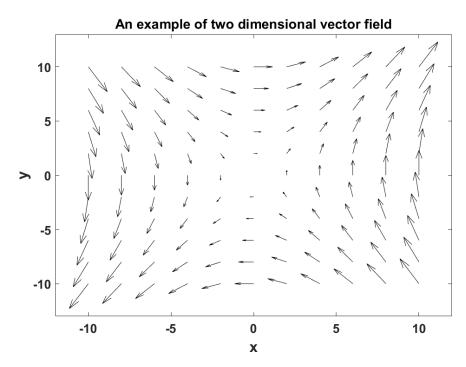

| Figure 5.7  | An Example of a Two Dimensional Vector Field                             | 95  |

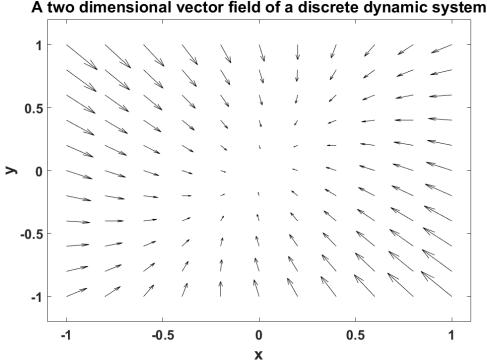

| Figure 5.8  | A Two Dimensional Vector Field of a Discrete Dynamic System              | 97  |

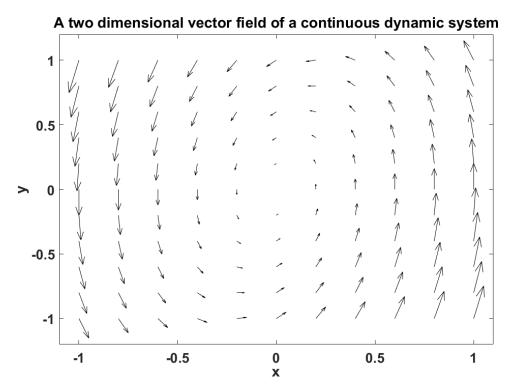

| Figure 5.9  | A Two Dimensional Vector Field of a Continuous Dynamic System            | 98  |

| Figure 5.10 | Bootstrapped Vt Reference Circuit's Two Dimensional Vector Field for     |     |

|             | Temperature Verification                                                 | 100 |

| Figure 5.11 | Van Kessel-Banba Circuit's Two Dimensional Vector Field                  | 102 |

| Figure 5.12 | Implementation of Breaking Loop of the Van Kessel-Banba Circuit $\ .$ .  | 104 |

| Figure 5.13 | Circuit Graph of Breaking Loop of the Van Kessel-Banba Circuit $\ . \ .$ |     |

| Figure 6.1  | An Example of SCC & BPSet                                                | 108 |

| Figure 6.2  | Flow of Proposed Verification Method                                     | 110 |

| Figure 6.3  | ITV Verification Flow                                                    | 111 |

| Figure 6.4  | ITV Menu Item in Cadence Virtuoso Schematic Editor                       | 112 |

| Figure 6.5  | SCC & BPSet Identification Form                                          | 114 |

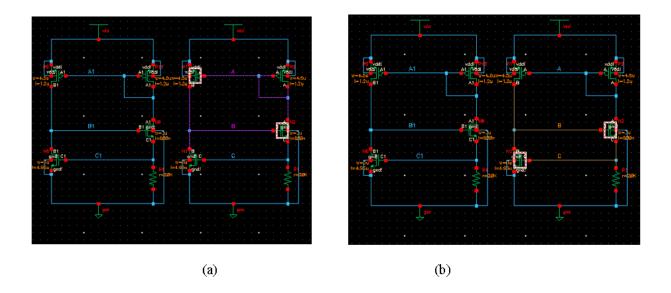

| Figure 6.6  | Obtain SCC: (a)Schematic with SCC0 Highlighted; (b)Highlight SCC0        |     |

|             | From the "SCC & BPSet Identification" Form                               | 116 |

| Figure 6.7  | Highlight Feedback Loops: (a) PFL of SCC0; (b) NFL of SCC0               | 117 |

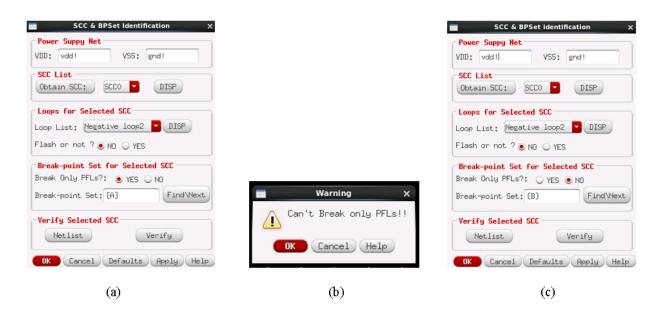

| Figure 6.8  | Select Break Points: (a)Only Break PFLs; (b)The Warning for "Can't       |     |

|             | Break Only PFLs"; (c)Break Both PFL and NFL                              | 118 |

| Figure 6.9  | ITV "Run Verification Settings" Form for B1P Circuits Stand-alone        |     |

|             | Verification                                                             | 119 |

| Figure 6.10 | ITV "Run Verification Settings" Form for B1P circuits PVT Verification   | 120 |

#### ACKNOWLEDGEMENTS

"Folk in those stories had lots of chances of turning back, only they didn't. They kept going, because they were holding on to something."

-J.R.R. Tolkien, The Two Towers.

It was a really hard journey for Frodo and Sam to finish their task of destroying the Ring at Mt Doom; similarly, it was the most difficult trip of my life to pursue my PhD degree at Iowa State University. As Frodo and Sam could not arrive at Mt Doom without the assistance of others, I would also like to attribute the completion of my PhD degree and this dissertation to those who helped me with various aspects of research and life in the past five years.

Foremost, I want to express my sincere gratitude to my advisor, Dr. Degang Chen, who offered me the opportunity to pursue my PhD degree, and guided me throughout my program. His rigorous scholarship and serious attitude to science deeply affected and always motivated me. His extensive knowledge and great insights often inspired me to see new ideas in research. I received many benefits from following his systematic and efficient work style. His guidance helped me in all my research and the writing of this thesis. I could not imagine finishing my PhD work without his mentoring and support.

I would also like to thank the rest of my thesis committee: Drs. Nathan M. Neihart, Chris Chong-Nuen Chu, Zhengdao Wang and Jaeyoun (Jay) Kim, for their encouragement, insightful comments, and stimulating questions. It has been a great experience to present my work to them and discuss it with them.

In the past five years, I made many good friends at Iowa State University; and I sincerely thank them for their help and companionship. I will never forget the classes we attended together, and the way they worked closely with me on struggling through projects; I also cannot forget the parties where we played together, and the funny moments I enjoyed with them. I will always remember those who supported me, Ames and Iowa State University.

There is a Chinese saying: A mother always worries about her traveling child. No matter how far away I am from home, my parents and sister always care for me and support me spiritually. I owe them a lot, and thank them for their love and support.

At the end of the story, Frodo and Sam saved their world after completing their journey to destroy the Ring. In my life, my five-year journey to pursue the PhD has greatly changed me, enriching my professional knowledge, building my life skills and strengthening my ability to face any difficulties. I feel confident as I start the next challenging journey in my life now.

We must keep running and hold on to our dreams!

#### ABSTRACT

Over the past 50 years, the integrated circuit (IC) industry has grown rapidly, following the famous "Moore's law." The process feature size keeps shrinking, whereby the performance of digital circuits is constantly enhanced and their cost constantly decreases. However, with the system integration and the development of system on chip (SoC), nearly all of today's ICs contain analog/mixed-Signal circuits. Although a mixed-signal SoC is primarily digital, the analog circuit design and verification consume most of the resources, and the dominant source of IC breakdowns is attributable to the analog circuits.

One important reason for the high cost and risk of breakdowns of analog circuits is that the technology advancement does not benefit many analog and mixed-signal circuits, and in fact imposes higher requirements on their performance. With process scaling, many important parameters of integrated circuit components degrade, which cause a drop in many key aspects of performance of analog circuits. Many analog circuits rely on matched circuit components (transistors, resistors, or capacitors) to achieve the required linearity performance; examples are amplifiers, digital-to-analog converters (DACs), etc. However, shrinking of the feature sizes increases the circuit components mismatch, thereby making it more difficult to maintain circuit accuracy.

Therefore, to reduce the cost of analog circuit design, designers should propose new structures whose key performance can be improved by the technology scaling. In this dissertation, we propose a low-cost, high-precision DAC structure based on ordered element matching (OEM) theory. High matching accuracy can be achieved by applying OEM calibration to the resistors in unary weighted segments and calibrating the gain error between different segments by calibration DAC (CalDAC). As a design example to verify the proposed structure, a high-precision DAC is designed in a 130 nm Global Foundry (GF) CMOS process. The 130 nm GF process features high-density digital circuits and is a typical process which is constantly enhanced by

the scaling of device dimensions and voltage supply; implementation of a high-precision DAC in such process is important to decreasing the costs of high-precision DAC designs. As a result, our proposed DAC structure is demonstrated to be able to significantly lower the cost of high-precision DAC design.

Another reason for the high cost and risk of breakdowns of analog circuits arises from the complexity of analog circuit working states. Most digital circuits serve as logic functions, so that digital transistors work in only two states, either low or high. In contrast, analog circuits have much more complicated functions; they may work in multiple operating points, since various feedback approaches are applied in analog circuits to enhance their performance. Circuits with undetected operating points can be devastating, particularly when they are employed in critical applications such as automotive, health care, and military products. However, since the existing circuit simulators provide only a single operating point, recognizing the existence of undesired operating points depends largely on the experiences of designers. In some circuits, even the most experienced designers may not be aware that a circuit they designed has undesired operating points, which often go undetected in the standard simulations in the design process.

To identify undesired operating points in an analog circuit and reduce its risk of breakdowns, a systematic verification method against undesired operating points in analog circuits is proposed in this dissertation. Unlike traditional methods of finding all operating points, this method targets only searches for voltage intervals containing undesired operating points. To achieve this, our method first converts the circuit into a corresponding graph and locates the break point to break all the positive feedback loops (PFLs). For one dimensional verification, divide and contraction algorithms could be applied to identify undesired operating points. Two dimensional vector field methods are used to solve the two dimensional verifications. Based on the proposed verification methods against undesired operating points, an EDA tool called "ITV" is developed to identify undesired operating points in analog and mixed-signal circuits. Simulation results show ITV to be effective and efficient in identifying undesired operating points in a class of commonly used benchmark circuits that includes bias generators, voltage references, temperature sensors, and op-amp circuits.

#### CHAPTER 1. INTRODUCTION

#### 1.1 Background

With the development of the IC industry, the mixed-signal SoC, which integrates all components of a computer or other electronic systems, has become more and more widely used. It may contain digital circuits, analog, mixed-signal, and other function blocks, all on a single chip. Compared with a combination of individual chips, an SoC has a great cost advantage. First, the SoC is much smaller because of its high integration. This allows the complete computer to be put into smart phones and tablets and still leave plenty of room for batteries. In addition, because of its very high level of integration and much less wiring, an SoC uses considerably less power, which is a big advantage for mobile computing. Moreover, decreasing the number of physical chips makes it much cheaper to build a computer or electronic system using an SoC [1]. Although an SoC is composed mainly of digital circuits, the analog circuit design and verification consumes more than 75 percent of the total resources [2]. Moreover, more than 78 percent of electronic breakdowns are due to the analog circuits [3]. The high cost and risks of breakdowns in analog circuits are due to the great differences in design and verification between analog and digital circuits.

Although the performance of digital circuits is constantly enhanced by the scaling of device dimensions and voltage supply, this technology advancement does not benefit many analog and mixed-signal circuits and in fact imposes higher requirements on their performance. With process scaling, many important parameters of the integrated circuit components degrade, which causes decreases in key performance of analog circuits. One important specification of analog circuits is their linearity, which is dependent on matched circuit components such as transistors, resistors, or capacitors. For example, linearity performance of amplifiers mainly relies

on the matching of their input transistor pairs. Another example is seen in the high-precision digital-to-analog converter (DAC), which relies on matched resistor arrays to perform its data conversion tasks. However, the shrinking of feature sizes increases the circuit components mismatch [4], thereby requiring greater effort to maintain circuit accuracy. With process scaling, some analog circuits may maintain or improve their linearity performance by use of a larger die area or more complicated calibration circuits. However, other analog circuits, such as highprecision DACs can be implemented only by high-precision analog process, and can barely be compatible with the process features high-density digital circuits. Thus, it is impossible to integrate analog circuits such as high-precision DACs into an SoC system, and the cost of implementing such circuits is high and hardly benefits from the process scaling.

The high risk of the analog circuit arises from the complexity of its working states. Most digital circuits serve as logic functions, so that digital transistors work in only two states, either low or high, which makes tests for digital circuits easily standardized. Standard test technologies such as scan, JTAG, LBIST, MBIST are all widely used to address the digital circuit tests problem, which explains the low failure rate of digital circuits. In contrast, analog circuits have much more complicated functions; they amplify signals, stabilize the power supply, or convert digital signals to analog signals, among others. Because of the complicated functions of analog circuits, there is no standard way to test and verify them. Most of the analog tests depend only on the experience of test engineers, who have to write as many tests as possible to cover the specification in the time available and to maintain the test cost in a reasonable range relative to the selling price [3]. Since the analog test is by far the dominant test cost, it has even changed the role of analog circuit design engineers. Formerly, they focused only on circuit designs, but now they must be involved in numerous analog circuit designs and verification to reduce the test costs. However, even with the help of circuit designers, some analog circuit test and verification problems still cannot be detected, resulting in circuit failures.

The existence of multiple operating points is one of the most important, although often ignored, problems in analog circuit test and verification. While various feedback approaches, e.g., self-biasing [5], bootstrapping [6], and digitally-assisted-analog [7] have been applied to analog circuits, these may make a system vulnerable to multiple operating points. The exis-

tence of undetected operating points can be devastating, particularly in circuits employed in critical systems such as automotive, health care, and military products. However, since the existing circuit simulators provide only a single operating point [8], recognizing the existence of undesired operating points largely depends on the experience of designers. In some circuits, even the most experienced designers are not aware that a circuit they designed has undesired operating points, which often go undetected in the standard simulations in the design process. Since most analog circuits are not kept in constant working environment now, and because of Process/Voltage supply/Temperature (PVT) variations, the existence of undesired operating point may be detected. It can be very costly if an undesired operating point in the circuit is first detected in the field by a customer. On the other hand, more and more basic circuits are being designed by new graduates or inexperienced analog engineers and circuit designers who continuously adding "smart components" in their design utilizing feedback. Consequently, undesired operating points are becoming an increasingly widespread and insidious problem plaguing the circuit design industry.

#### 1.2 Contribution of this Dissertation

To reduce the cost of analog circuit design, designers should propose new structures whose key performance can be improved by the technology scaling. In this dissertation, we use the high-precision DAC circuit as a low-cost design example and propose a low-cost, high-precision DAC structure based on OEM theory. The DAC is one of the circuits for which demands for high-accuracy requirements are increasing in precision medical, instrumentation, and test and measurement applications. The existing high-precision DACs require a large die area, high-precision analog process, advanced resistor trimming technique, complicated calibration circuits and additional test costs. As a result, their cost is high and difficult to reduce, since their implementation can hardly benefit from the scaling of digital circuits.

Random mismatch errors in resistor networks are dominant nonlinearity sources in high resolution and high accuracy resistor DACs. It has been rigorously proven and verified that ordered element matching (OEM) technology could significantly reduce the random mismatch errors and improve the linearity performance of DACs. More importantly, implementation

of this technique relies on digital circuits only, and its test method is consistent with the traditional INL test, making it a very prosperous technique of implementing a low-cost, high-precision DAC. In this dissertation, a low-cost, high-precision DAC structure based on OEM theory is proposed. It can achieve high matching accuracy by applying the OEM calibration to the resistors in unary weighted segments and calibrating the gain error between different segments by calibration DAC (CalDAC).

As a design example to verify the proposed structure, a high-precision DAC is designed in a 130 nm Global Foundry (GF) CMOS process. The 130 nm GF process features highdensity digital circuits but lacks high-precision resistors or any resistor trimming techniques, making it generally unsuitable for any high-precision DAC design. However, we implemented our design in such process from a behavioral model to a schematic and a layout design. The simulation and measurement results show the proposed DAC structure can greatly reduce the area requirement and make it possible to implement a high-precision DAC without use of a high-precision fabrication process. Since the 130 nm GF process is a typical process that is constantly enhanced by the scaling of the device dimensions and voltage supply, implementation of a high-precision DAC in such a process is an important means of decreasing the cost of highprecision DAC design. As a result, our proposed DAC structure is demonstrated to be able to significantly lower the cost of high-precision DAC design.

To reduce the cost and risk of breakdowns of analog circuits, identifying and removing undesired operating points is one of the most important problems. In this dissertation, a divide and contraction verification method against undesired operating points in analog circuits is proposed. Unlike traditional methods to find all operating points, this method searches for only the voltage intervals containing undesired operating points. To achieve this, a systematic approach to automatically identifying all positive and negative feedback loops in circuits is introduced. A positive feedback loop breaking method and selection of breaking nodes are discussed to determine whether a monotonic return function can be obtained. Depending on the monotonicity of the return function, two types of divide and contraction algorithms are proposed to efficiently search for voltage intervals containing operating points.

In practice, designers also need to verify circuits with transistor sizing, PVT variations; or identify the existence of undesired operating point in complicated circuits (B2P circuits). This type of problems is called the two dimensional analog verification against undesired operating points. For this type of verification, a two dimensional vector field method is proposed that can effectively identify the existence of undesired operating points by visualizing the return functions in the circuits.

Based on the proposed verification methods used against undesired operating points, an EDA tool called "ITV" is developed to identify undesired operating points in analog and mixed-signal circuits. It can accomplish this on the basis of the break-loop Homotopy method. It first converts the circuit into a corresponding graph and locates the break point to break all of the positive feedback loops (PFLs). It then searches the voltage intervals that contain undesired operating points by use of divide and contraction algorithms or the two dimensional vector field method. Simulation results show ITV to be effective and efficient in identifying undesired operating points in a class of commonly used benchmark circuits, including bias generators, voltage references, temperature sensors, and op-amp circuits.

#### 1.3 Organization of this Dissertation

This dissertation is organized as follows: Chapter 2 provides the proposed low-cost, highprecision DAC structure and its design methodology. In Chapter 3, design and measurement of a high-precision DAC based on the proposed structure is presented. Chapter 4 then develops a high efficient divide and contraction method to verify the existence of undesired operating points in analog circuits. To accomplish the two dimensional analog verifications, Chapter 5 proposes a two dimensional vector field method. In Chapter 6, an EDA tool called "ITV" is introduced to implement the proposed methods of identifying the undesired operating points in analog circuits. Finally, conclusions are presented in Chapter 7.

## CHAPTER 2. LOW-COST, HIGH-PRECISION DAC DESIGN BASED ON ORDERED ELEMENT MATCHING

#### 2.1 Introduction

Until now, the performance of digital circuits has been constantly enhanced by the scaling of device dimensions and voltage supply. However, the technology advancement does not benefit many analog and mixed-signal circuits and in fact it imposes higher requirements on their performance. The digital-to-analog converter (DAC) is one of the circuits seeing a demand for increased high accuracy in precision medical, instrumentation, and test and measurement applications [9]. High-precision 12-bit DACs were once considered to be difficult to implement; however, 16-bit accuracy is now widely used in high-precision applications. Recently, even a 20-bit, 1-ppm-accurate DAC integrated circuit was proposed to meet the needs of the precision instrumentation market [10].

Most high-precision DACs rely on accurate resistor arrays to perform data conversion tasks, so their accuracy is very sensitive to the matching performance of the resistor networks. However, the integrated-circuit (IC) fabrication technology cannot produce perfectly matched resistors, and with the process scaling, the random mismatch errors increase significantly [11, 12]. Therefore, implementing a high-precision DAC is very costly and depends on many different techniques.

The most important cost in achieving a high-precision DAC is the resistor area on the chip. In general, 1-bit linearity enhancement leads to quadrupling of the circuit area [13]. Nevertheless, the maximum allowed area is limited by the available die size as growing numbers of circuits and systems are integrated into a single chip. Therefore, the implementation of a high-precision DAC requires high-precision analog processes with high-precision resistors, such

as silicon-chromium thin-film resistors [10]. Unfortunately, such processes are usually associated with large transistor feature size and do not scale.

Aside from the resistor area, resistor trimming is often applied to achieve a high-precision DAC, which also demands high cost. Popular trimming techniques are divided into two main categories: laser trimming and fuse trimming [14, 15]. Laser trimming employs laser beams to accurately adjust the resistor parameters at the wafer level, while fuse trimming utilizes a fuse or anti-fuse for opening or closing the interconnections of a network of resistive elements intended to minimize mismatch errors. However, trimming techniques usually require high expenses such as extra layers or more die area for trim pads, and the achieved accuracy is reduced by temperature and aging effects [14].

High-accuracy calibration circuits are usually employed in high-precision DACs. They decrease the mismatch errors by either digital or analog feed-back signals from error-measuring circuits, such as a high-resolution high-accuracy analog-to-digital converter (ADC) [16, 17] or DAC [18, 19, 20]. However, the price of implementing those calibration circuits is high. It requires accurate measurement and complicated feedback circuits, which occupy a large silicon area, especially for high-precision analog processes whose feature sizes are large. In addition, specific calibration tests, other than the general DAC tests, are required to implement the calibration, making the expense of calibration circuits even higher.

Dynamic element matching (DEM) is another popular means of implementing a highprecision DAC. It dynamically changes the positions of mismatched elements at different times so that the equivalent component at each position is nearly matched on a time average. Several popular DEM algorithms are available, such as butterfly randomization [21], individual level averaging [22], and data weighted averaging [23]. Unlike the static random mismatch compensation techniques, DEM translates mismatch errors into noise. However, the translated noise is only partially shaped where the in-band residuals could possibly affect the data converters signal-to-noise ratio (SNR) [24]. Furthermore, the output will be inaccurate at one instant of time, since DEM guarantees matching only on average, so that its applications are limited to sigma delta modulators.

In summary, existing high-precision DACs require a large die area, high-precision analog processes, advanced resistor trimming techniques, complicated calibration circuits and additional test costs. As a result, their cost is high and difficult to reduce, because their implementation benefits very little from the scaling of digital circuits.

A different approach, called ordered element matching (OEM), was proposed in [25, 13, 26, 27] to implement high-precision DACs. The OEM technique can significantly reduce random mismatch errors and improve the linearity performance of DACs. More importantly, its implementation relies only on digital circuits and the test method is consistent with traditional INL tests [27], making it a very promising technique of implementing a low-cost, high-precision DAC. Based on the OEM technique, a high-precision segmented DAC structure has been introduced in [28] and has achieved accuracy of about 20-bit from the MATLAB simulation. Nevertheless, its implementation needs additional switch circuits to calibrate the gain errors between different segments, which requires extra circuits area and may cause leakage problems.

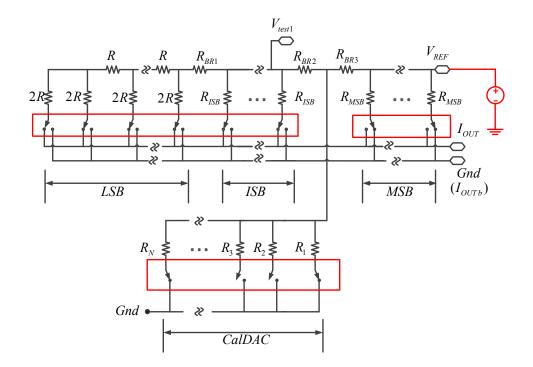

In this dissertation, a low-cost, high-precision DAC structure based on the OEM technique is presented. It consists of three segments: binary weighted least significant bits (LSB), unary weighted intermediate significant bits (ISB) and most significant bits (MSB). The optimized OEM process is applied to the unary weighted ISB and MSB segments. A sub-radix-2 calibration DAC (CalDAC) is implemented to calibrate the gain errors between ISB and MSB segments. On the basis of a 130 nm CMOS technique, a high-precision DAC is implemented to demonstrate the design methodology of the proposed DAC structure.

This chapter is organized as follows. In section 2, the proposed high-precision DAC structure based on OEM is introduced; section 3 discusses the design of the gain calibration pseudo DAC included in the proposed DAC structure; section 4 illustrates the OEM calibration process and implementation; behavioral simulation results are provided in section 5, and conclusions are stated in section 6.

In this section, a low-cost, high-precision DAC structure based on OEM is illustrated. First, the OEM technology used for reducing the mismatch error is introduced. Then a segmented high-precision DAC structure is proposed and analyzed. To minimize the gain error between different segments, a gain calibration DAC (CalDAC) is integrated into the proposed DAC structure and its design is discussed. The process of applying OEM calibration and its implementation in digital circuits are then interpreted.

#### 2.2.1 OEM Technology

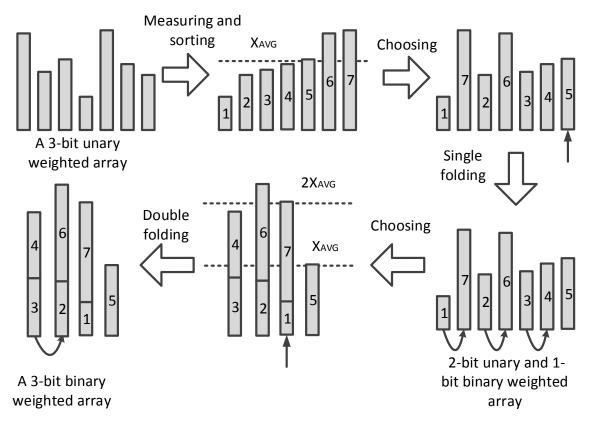

Fig. 2.1 shows the process of OEM technology. Each rectangle denotes a component with random mismatch errors in the unary-weighted segment. Component can be a resistance, conductance or any other amplitude whose random mismatch errors are targeted to be minimized [29], with  $X_{AVG}$  as the average amplitude. First, all components are measured and sorted according to their amplitudes. The second step is to choose the component with amplitude closest to  $X_{AVG}$ . Third, complementary ordered components are paired, which is called one "folding". The original 3-bit unary coded component array is converted into a 2-bit unary-weighted and 1-bit binary-weighted array. In detail, the amplitude of each 2-bit unary weighted array is nearly twice of the  $X_{AVG}$ , and the random variations in the components are reduced. Mismatch errors consistently diminish after each choosing and folding operation. As shown in Fig. 2.1, if the choosing and single folding operations are repeated until the 3-bit unary weighted array is converted into a 3-bit binary weighted array, mismatch errors are further reduced. This process is called "OEM binarization."

Figure 2.1: OEM Binarization

#### 2.2.2 High-precision DAC Structure

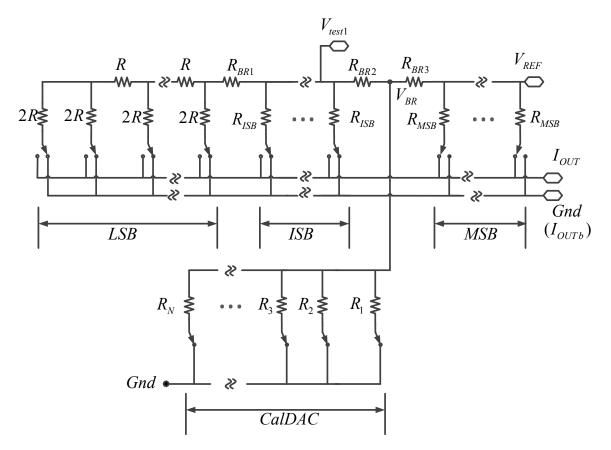

Fig. 2.2 shows the proposed high-precision DAC structure based on OEM. Although the design requires an external feedback resistor that creates noise and endpoint errors [10], the commonly called current-mode R-2R ladder network DAC is selected, for the following reasons. First, the current-mode structure avoids the resistor non-linearity caused by self-heating, which is the dominant contributor to resistor non-linearity [30]. In the voltage mode R-2R ladder network, different currents flow through different resistors and the currents vary with the DAC codes, causing the non-linearity problem. In contrast, all resistors in the same segment of the current mode R-2R ladder network have the same current, which do not change with the DAC codes. Thus, self-heating will not cause non-linearity errors in the current-mode structure, saving the cost of calibrating the resistor non-linearity that is due to self-heating. The second reason to use the current-mode structure is to minimize the INL error caused by unequal re-

Figure 2.2: Proposed OEM Based High-precision DAC Structure

sistance in switch pairs. In a voltage-mode structure, pairs of PMOS and NMOS switches are usually used. To minimize the INL error due to the different on-resistance between PMOS and NMOS, techniques [31] and[10] are needed, requiring high-performance amplifiers and other circuitry on the chip for high-precision DACs. However, the current-mode structure uses pairs of NMOS switches, whose on-resistance difference can be minimized by using common-centroid layout techniques and reasonable switch areas. As a result, the current-mode structure is preferable for a low-cost, high-precision DAC design. Endpoint errors associated with the external feedback resistor can be minimized by using high-accuracy feedback resistors. Assuming the high-precision DACs are mostly used in pseudo DC applications, the noise problem caused by the external feedback resistor is negligible, since the bandwidths of high-precision DACs are narrow.

To meet the linearity target of DACs, the area requirements of resistors are often calculated by the resistors matching level, as shown in the following subsection. The matching level of the resistance of a resistor is the same as its corresponding conductance, as shown in

$$G = \frac{1}{R} \Rightarrow \Delta G = \frac{-\Delta R}{R^2} \Rightarrow \frac{\Delta G}{G} = -\frac{\Delta R}{R}$$

(2.1)

where resistance R is the resistance of a resistor and G is its corresponding conductance. Yet, the mismatching level of resistors is easily found in a process design manual instead of their corresponding conductance mismatching level. As a result, resistors in ISB and MSB segments are marked  $R_{ISB}$  and  $R_{MSB}$  in Fig. 2.2. However, because the proposed DAC is a current output DAC, its linearity performance is determined by the output current relationship with the DAC input codes. In the unary weighted segments, the resulting output current of each resistor is determined by its conductance. For instance, the output current generated by the *ith* MSB resistor is  $I_{out(i)} = V_{REF}/R_{MSB(i)} = V_{REF} \times G_{MSB(i)}$ . As a result, OEM binarization should be applied to conductances rather than resistances of ISB and MSB segments to improve their linearity performance.

The proposed DAC structure consists of three segments: the binary weighted LSB, unary weighted ISB and MSB. Compared with the traditional two-segment DAC structure [10], the proposed DAC structure achieves higher linearity performance by application of OEM binarization to both the ISB and MSB segments. A unary weighted array with more than 7 bits requires digital circuits that are too complicated for OEM binarization to be applied to. OEM binarization cannot be utilized in binary weighted array, and LSB segment accomplishes its targeted accuracy through the resistor's intrinsic matching. For a 16  $\sim$  20 bit high-precision two-segment DAC structure, the intrinsic matching of the resistors in the binary weighted LSB should be above the 9 to 13 bit level, assuming the MSB segment is 7-bit and calibrated by OEM binarization. However, resistors with a 9 to 13 bit matching level require large areas if high-precision analog processes are not being used. Thus another unary weighted ISB segment is needed in high-precision DAC design. By applying OEM binarization to both the ISB and MSB segments, the matching level of resistors in the two segments can be significantly improved [28]. Moreover, the requirement of intrinsic matching level of resistors in the LSB segment is

greatly relaxed, thereby reducing the area of LSB resistors. For example, a 20-bit DAC with 5-bit ISB and 7-bit MSB requires only 8-bit matching resistors in the LSB segment, which significantly decreases the area of the LSB segment and the total area of the DAC. However, adding the ISB segment into the DAC produces a gain error problem between the ISB and MSB segments, which can be minimized by a gain calibration method discussed in the next section.

#### 2.2.3Segmentation Choices

For the proposed DAC structures, the segmentation choice should be carefully considered. First, resistors in different segments do not have the same effect on DAC linearity performance. In INL, the contribution of LSB resistor non-linearity could be approximated as

$$INL_{(R_{LSB})} = 2^{nlsb-0.5} \times \sigma_{R_{LSB}} \tag{2.2}$$

where  $\sigma_{R_{LSB}}$  is the standard deviation of the LSB resistor random mismatch error, and *nlsb* is the number of LSB segment bits. Although the current-mode structure is applied in the design, the variation of the output current depends mainly on the difference between resistors.

The contribution of the ISB and MSB resistors non-linearity could also be separately estimated as

$$INL_{(R_{ISB})} = 2^{nlsb+nisb/2+0.5} \times \sigma_{R_{ISB}}$$

$$\tag{2.3}$$

$$INL_{(R_{MSB})} = 2^{nlsb+nisb+nmsb/2+0.5} \times \sigma_{R_{MSB}}$$

$$\tag{2.4}$$

where  $\sigma_{R_{ISB}}$  is the standard deviation of the ISB resistor random mismatch error,  $\sigma_{R_{MSB}}$  is the standard deviation of the MSB resistor random mismatch error, *nisb* is the number of ISB bits and nmsb is the number of MSB bits.

After applying the OEM process as described in sub-section 1.2.2, the resulting INL caused by random mismatch errors in ISB/MSB segments is modeled as

$$INL'_{(R_{ISB})} = 2^{nlsb + nisb/2 + 0.5 - X1} \times \sigma_{R_{ISB}}$$

(2.5)

$$INL'_{(R_{MSB})} = 2^{nlsb+nisb+nmsb/2+0.5-X2} \times \sigma_{R_{MSB}}$$

(2.6)

www.manaraa

#### 13

#### www.manaraa.com

| Bit number          | 5   | 6   | 7   |

|---------------------|-----|-----|-----|

| x1                  | 3   | 4   | 4.5 |

| x2 (w/20%  outlier) | 4.5 | 5.5 | 7   |

Table 2.1: OEM Reduction Factor

where X1 and X2 are called OEM INL reduction factors. For the MSB segment, an outlier elimination technique is used to further improve the matching performance [13], and about 20% being the best percentage of outlier number. The OEM INL reduction factors vary with process and resistor areas, but their approximate values can be obtained as shown in TABLE 2.1.

The required area of resistors is estimated from the standard deviation of their mismatch error

$$A_{req} = A_u (\frac{\sigma_u}{\sigma_{req}})^2 \tag{2.7}$$

where  $\sigma_u$  is the standard deviation of unit resistor,  $\sigma_{req}$  is the required standard deviation of the mismatch errors, and  $A_u$  is the area of unit resistor. From equations (2.2) (2.5) (2.6) (2.7), the total area can be estimated as follows:

$$A_{total} = \left(A_u \left(\frac{\sigma_u}{\log_2(INL_{MSB}/2^{nlsb+nisb+nmsb/2+0.5-X2})}\right)^2 + A_{Digital} + A_{SW_{MSB}}\right) \\ \times (2^{nmsb} - 1) \times 1.2 + \left(A_u \left(\frac{\sigma_u}{\log_2(INL_{ISB}/2^{nlsb+nisb/2+0.5-X1})}\right)^2 + A_{Digital} + A_{SW_{ISB}}\right) \\ \times (2^{nisb} - 1) + \left(A_u \left(\frac{\sigma_u}{\log_2(INL_{ISB}/2^{nlsb-0.5})}\right)^2 + A_{SW_{LSB}}\right) \times (3nlsb+1)$$

(2.8)

where  $A_{Digital}$  is the OEM digital circuit for each resistor (illustrated in section 4),  $A_{SW_{MSB}}$ ,  $A_{SW_{ISB}}$  and  $A_{SW_{LSB}}$  are the single switch areas for the MSB, ISB and LSB segments, respectively.

Equation (2.8) shows more unary weighted bits (more bits in the ISB and MSB segments) the linearity performance further improves, decreasing the area of resistors. However, with more unary-weighted bits, more digital circuits are required to implement OEM. Thus a trade-off exists between the digital circuit and the resistor area when segmentation is performed.

Another important consideration related to segmentation is power consumption. The power consumption of a DAC is

$$P = V_{ref}^2 / R_{output} \tag{2.9}$$

where  $R_{output} = R_{msb}/2^{nmsb}$  is the output impedance of the DAC. Thus, the unit resistor value and the number of bits in the MSB segment are limited by power consumption. In most general analog processes, resistors with higher matching performance usually have lower resistance density. The large  $R_{output}$  needed to reduce power consumption may cause large area requirements for resistors with high matching performance but low resistance density. On the other hand, with one more bit in the MSB segment, the required resistance of the MSB resistor doubles for the same power consumption. Therefore, the number of bits in the MSB segment should be carefully selected, not only on the basis of the matching level to be achieved, but also on the basis of power consumption limitations.

#### 2.3 Gain Calibration Pseudo DAC Design

#### 2.3.1 Gain Error between Different Segments

Aside from mismatch errors in each segment, an important non-linearity error in the segmented DAC is the gain error between different segments. For example, in an ideal matched three-segment DAC, the following relation exists between the ISB and MSB segments:

$$V_{ref}G_{ILSB}(2^{N-nmsb}) = V_{ref}G_{MSB}(1)$$

$$(2.10)$$

where N is the total bits of the DAC, nmsb is the bits of MSB segment,  $G_{MSB}(1) = (R_{MSB(1)})^{-1}$ is the conductance of the lowest bit of MSB segment, and  $G_{ILSB}(2^{N-N_{msb}})$  is the total conductance of the LSB and ISB segments. The gain error between the ISB segment and the MSB segment from (2.10) generates the following output current:

$$\Delta I_{Gain} = V_{ref}(G_{ILSB}(2^{N-nmsb}) - G_{MSB}(1)) = V_{ref}\Delta G.$$

(2.11)

Since the lowest bit of MSB stands for  $2^{N-nmsb}$  LSB of the whole DAC, the following equation is required to make the total INL error less than 1 LSB:

$$|\Delta I_{Gain}| < \frac{I_{MSB}(1)}{2^{N-nmsb}}.$$

(2.12)

Similar analysis is applied to the gain error between the ISB and LSB segments. Gain error between different segments must be minimized in a high-precision DAC.

In the structure proposed in [28], gain calibration is achieved by changing different bridge resistors, and both the gain error between the LSB and ISB segments and the gain error between ISB and MSB segments are calibrated. Nevertheless, its implementation needs additional switch circuits to calibrate the gain errors between different segments, causing additional circuit area and potential leakage problems. Moreover, the gain error between the LSB and ISB segments can be minimized by increasing the area of the  $R_{br1}$ , and the gain error between the ISB and MSB segments is the dominant gain error. As a result, in the proposed DAC structure shown in Fig. 2.2, no additional switches in the unary weighted segments to calibrate the gain errors between different segments are used. Instead, the gain error between LSB and ISB is minimized by enlarging the area of the  $R_{br1}$ , and a calibration pseudo DAC (CalDAC) is inserted between the ISB and MSB segments for calibrating the gain errors.

#### 2.3.2 Gain Calibration DAC

The results of (2.11) and (2.12) are

$$|\Delta G| = |G_{ILSB}(2^{N-nmsb}) - G_{MSB}(1)| < \frac{G_{MSB}(1)}{2^{N-nmsb}},$$

(2.13)

creating,

$$G_{MSB}(1)(1 - \frac{1}{2^{N-nmsb}}) < G_{ILSB}(2^{N-nmsb}) < G_{MSB}(1)(1 + \frac{1}{2^{N-nmsb}}) \Rightarrow -\frac{1}{2^{N-nmsb} + 1} R_{MSB(1)} < R_{ILSB}(2^{N-nmsb}) - R_{MSB}(1) < \frac{1}{2^{N-nmsb} - 1} R_{MSB}(1)$$

(2.14)

where  $R_{ILSB}(2^{N-nmsb}) = (G_{ILSB}(2^{N-nmsb}))^{-1}$  and  $R_{MSB}(1) = (G_{MSB}(1))^{-1}$ .

Assuming  $2^{N-nmsb} >> 1$ , (2.14) is simplified to

$$|R_{ILSB}(2^{N-nmsb}) - R_{MSB}(1)| = |\Delta R| < \frac{1}{2^{N-nmsb}} R_{MSB}(1)$$

(2.15)

From (2.15), the gain error is reduced to meet the DAC accuracy requirement if  $|\Delta R|$  is calibrated to the required level.

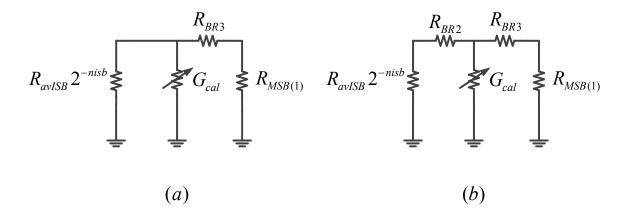

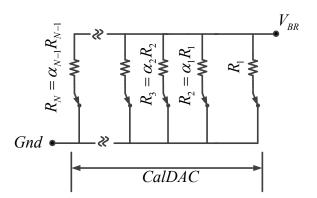

Figure 2.3: (a) First Simplified CalDAC Structure; (b) Second Simplified CalDAC Structure.

Fig. 2.3 shows a comparison of two types of pseudo calibration DAC structures. In the first simplified pseudo calibration DAC structure, shown in Fig. 2.3(a),  $R_{avISB}$  is the average value of all the resistors and switch on-resistances in the ISB segment, *nisb* is the bits of the ISB segment,  $G_{cal}$  is the conductance of the CalDAC, and  $R_{MSB(1)}$  is the lowest bit resistance of the MSB segment. In this structure,

$$R_{ILSB}(2^{N-nmsb}) = R_{BR3}G_{cal}2^{-nisb}R_{avISB} + 2^{-nisb}R_{avISB} + R_{BR3}$$

$$= R_{BR3}G_{cal}2^{-nisb}R_{avISB} + R_{T1}$$

(2.16)

where  $R_{T1} = 2^{-nisb}R_{avISB} + R_{BR3}$ .

By setting  $R_{ILSB}(2^{N-nmsb})|_{nom} = R_{T1}$ , the gain error can be reduced to our required accuracy by tuning  $G_{cal}$  to minimize  $\Delta R$ ; or we can make

$$R_{ILSB}(2^{N-nmsb})|_{nom} = R_{BR3}G_{cal}|_{nom}2^{-nisb}R_{avISB} + R_{T1} = R_{MSB(1)}$$

(2.17)

where  $G_{cal}|_{nom}$  is the nominal value of the  $G_{cal}$ . Both cases require  $R_{T1} < R_{MSB(1)}$ .

The second simplified CalDAC structure is shown in Fig. 2.3(b); its  $R_{ILSB}(2^{N-nmsb})$  is calculated as

$$R_{ILSB}(2^{N-nmsb}) = R_{BR3}G_{cal}(2^{-nisb}R_{avISB} + R_{BR2}) + 2^{-nisb}R_{avISB} + R_{BR2} + R_{BR3}$$

$$= R_{BR3}G_{cal}(2^{-nisb}R_{avISB} + R_{BR2}) + R_{T2}.$$

(2.18)

where  $R_{T2} = 2^{-nisb}R_{avISB} + R_{BR2} + R_{BR3}$ . As is the case for the first structure, the gain error can be minimized by  $G_{cal}$ .

From (2.16) and (2.18), the  $\Delta R$  is calibrated to the required accuracy by tuning  $G_{cal}$ , thereby reducing the gain errors in both CalDAC structures. However, the required calibration ranges for these two CalDAC structures differ greatly.

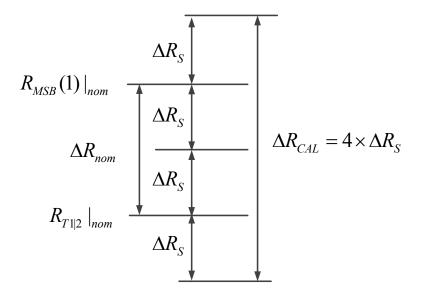

Assuming the standard deviation of  $R_{MSB}(1)$  variation is  $\sigma_{R_{MSB}(1)}$ , the largest variation of  $R_{MSB}(1)$  can be estimated as  $5\sigma_{R_{MSB}(1)} = \Delta R_S$ . With assignment of an area similar to  $R_{MSB}(1)$ , the largest variation of  $R_{T1}$  in the first structure and  $R_{T2}$  in the proposed structure are the same as  $\Delta R_S$ . The calibration range of CalDAC is analyzed as shown in Fig.2.4. Meeting the condition  $R_{T1} < R_{MSB(1)}$  and  $R_{T2} < R_{MSB(1)}$  in the two structures respectively requires that

$$R_{MSB}(1)|_{nom} - R_{T1/2}|_{nom} \ge 2\Delta R_S.$$

(2.19)

where  $R_{MSB}(1)|_{nom}$  is the nominal value of  $R_{MSB}(1)$ , and  $R_{T1/2}|_{nom}$  is the nominal value of  $R_{T1}$  or  $R_{T2}$ . Conditions (2.15) and (2.19) require the tuning range of  $G_{CAL}$  to calibrate the range

$$\Delta R_{CAL} \ge 4\Delta R_S. \tag{2.20}$$

Together with (2.16) and (2.18), the calibration range for the first CalDAC structure is:

$$\Delta G_{CAL1} \ge \frac{4\Delta R_S}{R_{BR3} 2^{-nisb} R_{avISB}},\tag{2.21}$$

and the calibration range for the second CalDAC is:

$$\Delta G_{CAL2} \ge \frac{4\Delta R_S}{R_{BR3}(2^{-nisb}R_{avISB} + R_{BR2})}.$$

(2.22)

When (2.21) is compared with (2.22), the calibration range  $\Delta G_{CAL2} < \Delta G_{CAL1}$ , which results in a smaller CalDAC design; this is why the calibration DAC structure in Fig. 2.3(b) is used in the proposed DAC structure.

In addition to the calibration range, the calibration step of the CalDAC, i.e., the bits of CalDAC, should also be taken into consideration. Assuming  $\Delta R_S = \frac{1}{2^{N_k}} R_{MSB}(1)$ , to meet

Figure 2.4: CalDAC Range

(2.15), requires the number of codes in the CalDAC

$$N_G \ge \frac{4\Delta R_S}{\frac{1}{2^{N-nmsb}}R_{MSB}(1)} = 2^{N-nmsb-N_k},$$

(2.23)

and thus requires at least  $N-nmsb-N_k$  bits CalDAC to calibrate the gain error to the expected accuracy. In practice, extra bits should be added to compensate for the resistor tolerance and variations of processes and temperature.

#### 2.3.3 Implementation of Gain Calibration

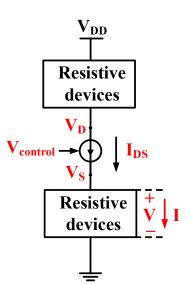

In sub-section 1.3.2, gain calibration was discussed; however, its implementation needs to be further investigated. From (2.22) and (2.23), the required calibration range and number of bits can be calculated, respectively. However, there is no linearity requirement for the CalDAC, because it works as a pseudo DAC and its input code is fixed after the best gain calibration. Thus, a sufficiently large calibration range with enough number of calibration steps are enough for implementation the required CalDAC. The most efficient way to implement the CalDAC is to employ the sub-radix-2 DAC, as shown in Fig. 2.5. The output of the CalDAC is connected to node  $V_{BR}$ , as shown in Fig. 2.2.

Figure 2.5: CalDAC Implemented As a Sub-radix-2 DAC

Figure 2.6: CalDAC Ratio

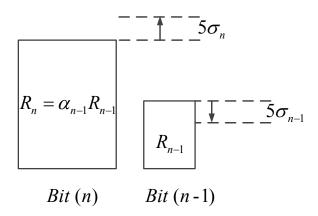

In CalDAC, each branch has a resistor and a switch. By connecting the switch to ground (Gnd), the corresponding bit contributes a conductance  $C_i = \frac{1}{R_i}$ . The ratio of the resistors between adjacent bits is  $\alpha_i < 2$ , e.g.  $R_2 = \alpha_1 R_1$ . The ratio  $\alpha_i$  between different bits is determined by the variations of resistance, as shown in Fig. 2.6. To make the ratio between adjacent bits less than two, the following relationship can be used:

$$\alpha_i R_{n-1} + 5\sigma_n < 2 \times (R_{n-1} - 5\sigma_{n-1}) \Rightarrow \alpha_i < 2 - (5\sigma_n + 10\sigma_{n-1})/R_{n-1}$$

(2.24)

where  $R_{n-1}$  is resistance of n-1 bit of CalDAC,  $\alpha_{n-1}$  is the resistance between  $R_n$  and  $R_{n-1}$ ,  $\sigma_n$  and  $\sigma_{n-1}$  are the standard deviation of resistance of n and n-1 bits of CalDAC, respectively.

Figure 2.7: The Gain Calibration Process

The gain calibration process is shown in Fig. 2.7. All the LSB and ISB resistors are connected to  $I_{out}$  and MSB resistors to Gnd. The CalDAC codes are swept from the smallest to the largest, and the total conductances of LSB and ISB segments for each CalDAC code i are obtained as  $G_{ILSB}(2^{N-nmsb})_{CALcode(i)}$ . The best CalDAC code which has the minimal value of  $|G_{ILSB}(2^{N-nmsb})_{CALcode(i)} - G_{MSB}(1)|$  among the different CalDAC codes, is selected. Therefore, the gain error can be calibrated by the CalDAC.

The gain calibration range ( $\Delta G_{CAL}$ ) of the CalDAC is determined by (2.22). Assuming that  $\Delta R_S$ ,  $2^{-nisb}R_{avISB}$  are defined from the segmentation choice,  $\Delta G_{CAL}$  is modified by changing the  $R_{BR2}$  and  $R_{BR3}$ . The number of bits for CalDAC (*ncsb*) is determined by (2.23). On this basis, the area of the CalDAC is analyzed as the following:

Without loss of generosity, we assume ncsb is a odd number, and the middle bit of the CalDAC is bit (ncsb+1)/2. To simplify the analysis, resistance ratios between adjacent bits  $\alpha_i$  are the same and equal to  $\alpha$ . Since CalDAC works as a pseudo DAC and there is no linearity requirement for the CalDAC, all resistors in the CalDAC can have the minimum width. As a result, the area of each bit depends on resistance density  $R_{\Box}$ ,  $\Delta G_{CAL}$  and ncsb. For example,

Table 2.2: Area of a 9-bit CalDAC

| Bit number          | Bit-9      | Bit-8      | Bit-7      | Bit-6 | Bit-5 | Bit-4      | Bit-3         | Bit-2         | Bit-1          |

|---------------------|------------|------------|------------|-------|-------|------------|---------------|---------------|----------------|

| Resistance<br>ratio | $\alpha^4$ | $\alpha^3$ | $\alpha^2$ | α     | 1     | $1/\alpha$ | $1/\alpha^2$  | $1/\alpha^3$  | $1/\alpha^4$   |

| Area<br>ratio       | $\alpha^4$ | $\alpha^3$ | $\alpha^2$ | α     | 1     | $4/\alpha$ | $16/\alpha^2$ | $64/\alpha^3$ | $256/\alpha^4$ |

the resistance of the middle bit is

$$R_{(ncsb+1)/2} = \frac{\alpha^{(ncsb+1)/2}}{\Delta G},$$

(2.25)

so its area requirement is calculated as

$$A_{(ncsb+1)/2} = \frac{\alpha^{(ncsb+1)/2}}{\Delta G R_{\Box}}.$$

(2.26)

The resistance of bit (ncsb+1)/2 + 1 should be  $\alpha R_{(ncsb+1)/2}$ , which can be implemented by combing two  $\alpha R_{(ncsb+1)/2}/2$  resistors series. Similarly, bit (ncsb+1)/2 + 1 is composed of four  $\alpha^2 R_{(ncsb+1)/2}/4$  resistors series, etc. The resistance of bit (ncsb+1)/2 - 1 is implemented as two  $2R_{(ncsb+1)/2}/\alpha$  resistors in parallel, and bit (ncsb+1)/2 - 2 implemented as four  $4R_{(ncsb+1)/2}/\alpha^2$ resistors in parallel. For example, the resistor and area ratio between different bits in a 9-bit CalDAC is summarized in TABLE 2.2. From (2.26), the total area of the CalDAC is calculated as

$$A_{CalDAC} = \left[\frac{1-\alpha^5}{1-\alpha} + \frac{4(\alpha^4 - 256)}{\alpha^5 - 4\alpha^4}\right] \frac{\alpha^{(ncsb+1)/2}}{\Delta GR_{\Box}}.$$

(2.27)

Assuming that  $\alpha = 1.8$ , ncsb = 9, and  $\Delta G = 1mS$ , changing the ratio between  $R_{BR2}$  and  $R_{BR3}$ from (2.22) results in an  $A_{CalDAC}$  of about  $1.226E6/R_{\Box}$ . In a general analog processes, the  $R_{\Box}$  of the poly resistor is  $1000 \sim 2000\Omega/\Box$ . Thus the  $A_{CalDAC}$  for a nine bit CalDAC is only  $613 \sim 1226R_{\Box}$ , which is small enough to be regarded as negligible compared with the area of the resistor array in the DAC.

# 2.4 OEM Calibration

#### 2.4.1 OEM Calibration

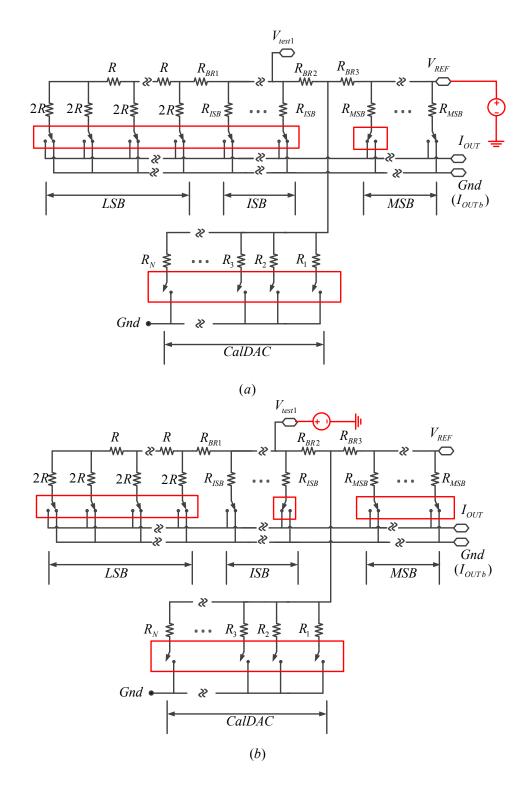

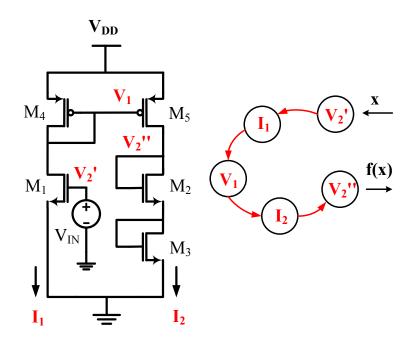

OEM calibration is applied to the resistances of the ISB and MSB segments in [28]. The calibration can be made more accurate by applying OEM calibration to the conductances of the ISB and MSB segments, because the proposed structure is that of a current output DAC. Moreover, since the CalDAC is employed to calibrate the gain error, the OEM calibration applied to the proposed DAC after fabrication is greatly simplified by following the steps shown in Fig.2.8.

Step 1 applies OEM binarization to the MSB segment. In this step, all resistors in LSB and ISB segments are switched to Gnd and all switches in the CalDAC are opened. Resistors in the MSB segment are sequentially switched to  $I_{out}$ , and the corresponding values of conductance  $G_{MSB(i)} = 1/R_{MSB(i)}$  are obtained one by one. From the measurement results of  $G_{MSB(i)}$ , OEM binarization can be applied to MSB conductances.

Step 2 is similar to Step 1 but applies the OEM binarization to the ISB segment. In this step, all resistors in LSB and MSB segments are switched to Gnd and all switches in the CalDAC are opened. Resistors in the ISB segment are sequentially switched to  $I_{out}$ , and the corresponding conductance values  $G_{ISB(i)} = 1/R_{ISB(i)}$  are obtained one by one. OEM binarization is then applied to the ISB conductances.

Figure 2.8: OEM Calibration Process: (a) Application of OEM Binarization to the MSB Segment; (b) Application of OEM Binarization to the ISB Segment

| Address Code | Number of components | Digital input |

|--------------|----------------------|---------------|

| 001          | 1                    | D[0]          |

| 010          | 2                    | D[1]          |

| 011          | 4                    | D[2]          |

| 100          | 8                    | D[3]          |

| 101          | 16                   | D[4]          |

| 110          | 32                   | D[5]          |

| 111          | 64                   | D[6]          |

Table 2.3: Digital Coding for OEM Binarization (7-bit)

#### 2.4.2 Digital Circuits to Implement OEM Calibration

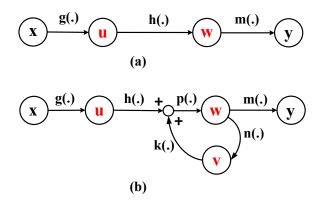

To implement OEM binarization, each resistor in a N-bit unary weighted segment needs to be connected to one of the N-bit lines. This requires an N-to-1 digital mux and a  $log_2N$  bit number of memories cells to store the mux address code for each element, similar to [26].

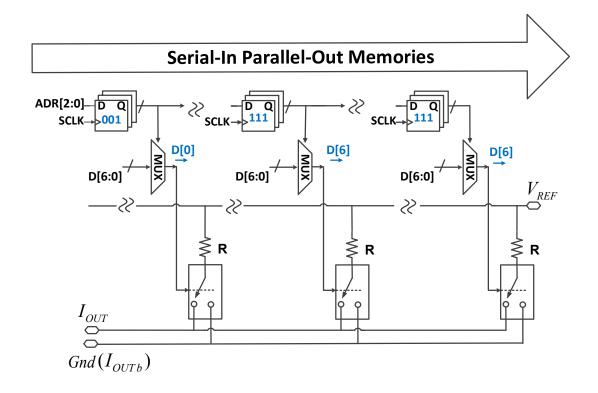

The calibration circuit for a 7-bit unary weighted segment is shown in Fig.2.9, where the OEM binarization is realized by the 3-bit memory cells and 7-bit muxes. The memory cells, which are arranged as serial-in parallel-out connections, can be either registers or one time programming (OTP) cells, depending on the application. TABLE 2.3 illustrates the corresponding address code and number of elements for different bit lines during the normal conversion phase. For example, if 010 is assigned to two resistors, D[1] will be selected to control them. With these arrangements, the 7-bit unary weighted segment operates in a binary weighted manner.

Figure 2.9: OEM Calibration Circuits

# 2.5 Behavioral Simulation Results

A MATLAB model of a 20-bit R-2R DAC with 8-5-7 segmentation was built on the basis of the proposed structure to verify its matching performance. We chose  $R_{msb} = 2R_{mid}$ ,  $R_{lsb} = R_{mid}$  and the same width for all resistors. To compare the model with state of the art models, the R-2R DAC model in [10] was also included, because it is the first and only one existing 20-bit R-2R DAC reported in the literature. It has a two-segment structure with 14-6 segments and could correct up to ±16 LSBs of INL by CALDAC.

First, the unit LSB in n bit level  $(LSB_n)$  was defined as

$$LSB_n = FS/2^n \tag{2.28}$$

where FS is the full scale of the DAC. If the matching level is the *n* bit, the standard deviation of the mismatch error  $\sigma \approx 1/2^n$ .

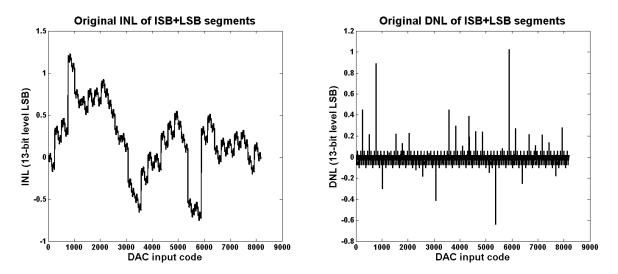

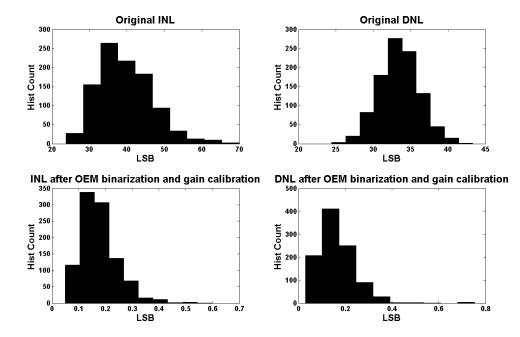

Figure 2.10: (a) INL Plot of the Original 13-bit LSB and ISB Segments; (b) DNL Plot of the Original 13-bit LSB and ISB Segments

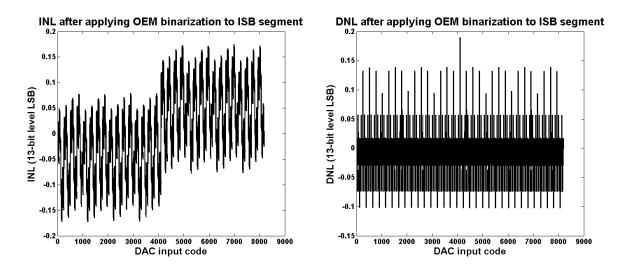

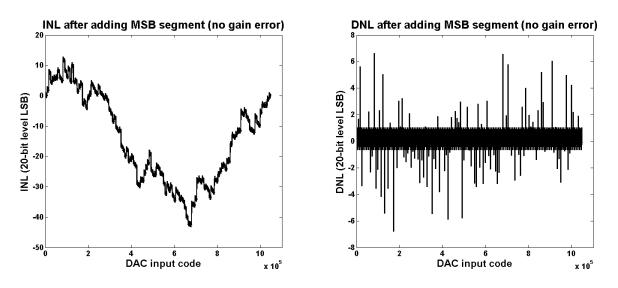

Fig. 2.10 shows the INL and DNL of a 13 bit DAC, which consists of only the 8 bit LSB and 5 bit ISB segments. The intrinsic matching level of the unit resistors in the ISB segment is about 8 bit, and the unit 2R resistor in the LSB segment has about 8 bit matching accuracy. As shown in Fig. 2.10 (a), the INL of the 13 bit DAC is about 1.2 *LSB* and the DNL is 1.1 *LSB*. It should be noted the LSB used here is in the 13 bit level. After OEM binarization is applied to the ISB segment, the INL was improved to about 0.18 *LSB* and the DNL improved to about 0.19 *LSB*, as shown in Fig. 2.11.

Figure 2.11: (a) INL Plot of the 13-bit LSB and ISB Segments After Applying OEM Binarization to the ISB Segment; (b) DNL Plot of the 13-bit LSB and ISB Segments After Applying OEM Binarization to the ISB Segment